基于ARM-WinCE平台的时钟同步设计

实现了以太网通信的驱动程序的基础上,用于时钟同步功能的应用程序通过UDP协议发送、接收时钟同步报文,并进行加入、提取和解析时间戳等操作,这些操作通过读写DP83640内部的1588基本寄存器组(PTP 1588 BASEREGISTERS)和1588配置寄存器组(PIP 1588CONFIGURATION REGISTERS)完成。

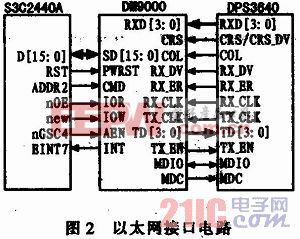

S3C2440A的数据线D[15:0]与DM9000的地址、数据复用数据线SD[15:0]连接用来实现S3C2440A与DM9000之间的数据传输。芯片选择信号AEN与S3C2440A的片选使能信号nGSC4连接,当访问0x20000000-0x27FF FFFF这个范围的地址时会激活片选使能信号nGCS4。DM9000默认I/O基地址为300H。CMD引脚用于设置COMMAND模式,与S3C2440A的ADDR2连接CMD为高电平时,选择数据端口。CMD为低电平时,选地址端口。数据端口和地址端口的地址码由下式决定:

DM9000地址端口=高位片选地址+300H+0H

DM9000数据端口=高位片选地址+300H+4H

高位片选地址由S3C2440A芯片的nGCS4提供,即为:0x20000000。因此DM9000的地址IO基址为0x20000000,数据IO基址为0x2000 0004。向地址IO写数据时不会激活ADDR2,CMD为低电平,所以向DM9000传送的数据为地址,而向数据IO写数据时会激活ADDR2,CMD为高电平,向DM9000传送的数据为数据。S3C2440的输出使能引脚nOE连接DM9000的读引脚IOR,写使能引脚nWE连接DM9000的写引脚IOW。DM9000的中断请求引脚INT连接S3C2440的外部中断请求引脚EINT7,使得S3C2440A能够响应DM9000的中断。

DM9000与DP83640之间通过标准MII接口连接,RXD[3:0]为接收数据线,TXD[3.0]为发送数据线,CRS为载波检测信号,COL为冲突检测信号,RX_DV为数据有效信号,RX_ER为接收错误信号,RX_CLK为接收时钟信号,TX_CLK为发送时钟信号,TX_EN为发送使能信号,MDIO是管理数据的输入输出双向接口,MDC为管理数据接口提供时钟信号。需要注意的是DM9000默认使用片内PHY,因此在驱动程序初始化DM9000时,必须主动置位网络控制寄存器NCR的EXT_PHY位以选择使用片外PHY即DP83640。

3 软件设计

软件设计分为两个步骤:1)是基于DM9000和DP83640进行以太网通信的驱动程序设计;2)是通过DP83640进行时钟同步的应用程序设计。

本文使用WinCE5.0操作系统,WinCE5.0系统下网络驱动程序的编写必须符合网络驱动接口规范NDIS(Network Driver Interface Stan dard)。NDIS的层次结构如图3所示,其中最上层的Winsock是提供给应用层的接口。NDIS位于协议驱动层下面,硬件驱动Miniport Driver之上。协议驱动层通过调用NDIS封装的接口函数,实现与底层硬件驱动的交互。WinCE下网络驱动程序的设计主要是在NDIS构架下,针对实际的硬件编写代码,实现相应的中间层Miniport Driver接口函数。其主要完成的功能有:DM9000与DP83640的初始化;网络数据包的发送;网络数据的接收和中断。

4 结论

IEEE1588协议通过在以太网上发送和接收同步报文来实现时钟同步,同步的精度取决于记录报文发送和接收时间的时间戳的精度,因此要实现高精度的时钟同步必须通过硬件支持在通信协议的底层加入和提取时间戳。本文通过在ARM-WinCE嵌入式系统平台上设计了使用DP836 40芯片作为PHY收发器的以太网接口电路及其驱动程序,实现了IEEE1588协议在ARM-WinCE平台上的移植,并达到了不低于1 μs的同步精度,为基于ARM-WinCE平台的测试仪器组建分布式测试系统奠定了基础。

同步 设计 时钟 平台 ARM-WinCE 基于 相关文章:

- 嵌入式同步时钟系统的设计与实现详解(05-19)

- 多通道同步数据采集及压缩系统(08-12)

- Mobileye获MIPS32 1004KTM同步处理系统授权(04-17)

- 基于DSP的高阶COSTAS锁相环的设计(03-02)

- 基于Android系统的影音播放器开发(03-25)

- Linux多线程同步方法(07-29)