独立于硬件技术的XC166单片机的DSP程序优化方法

相关性排除

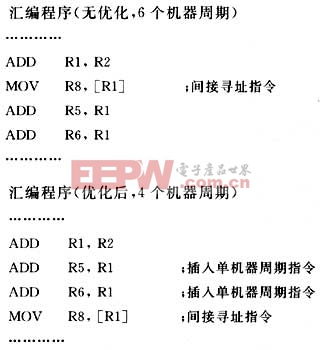

在XC166的CPU中,由于指令流水线的设计要求,在使用通用寄存器(GPRs)的指令之间存在一些数据相互依赖的情况,尽管XC166单片机已经使用了专用硬件来检测及解决数据相关性,但仍然有一些不可避免的数据相关性。在编程时,可以充分利用数据相关性来达到程序优化的目的,比如,在用GPR作为间接寻址指针时,如果PGR中的地址值被改变,间接寻址操作必须等待2个机器指令周期后,才能使用GPR作为地址指针寻址。在这种情况下,可以在这2个等待机器周期内插入2条其他单机器周期指令,充分利用这2个周期的等待时间以便程序更优化。

下面举一个例子:

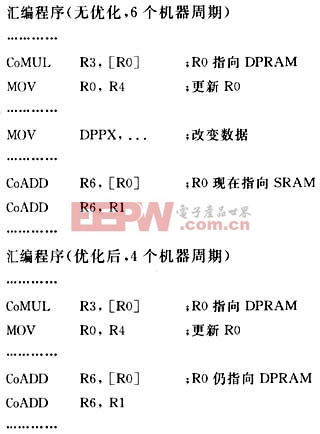

另外一种数据相关性发生在间接寻址访问内存时,XC166单片机中的地址产生单元使用推测原理,在地址译码前,数据的读取路经将根据历史记录表中选出;在历史记录表中,每个GPR都有一个入口。这些入口记录了用相应GPR所访问的内存空间情况。如果这种预测发生错误,读取操作必须重新开始。

因此,如果用GPR作为间接寻址,GPR最好能指向相同内存空间。如果更新后的GPR指向不同内存空间,下一个操作将出现访问错误,读操作必须重复,这就产生了指令流水线堵塞。例如:

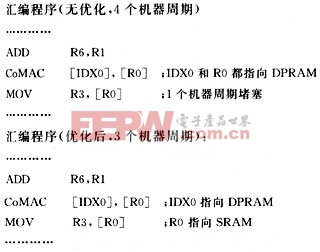

2.3 内存带宽冲突排除

如果在流水线上的指令在同一时间访问同一内存,就会发生内存带宽冲突,MAC单元的CoXXX指令是特别为实现DSP设计的。为了避免在DPRAM中发生带宽冲突,CoXXX指令的其中一个操作数必须放在SRAM中,以保证在单个机器周期内执行MAC单元指令。例如:

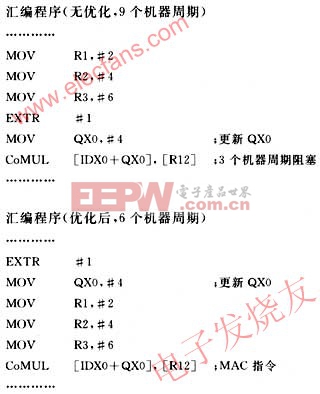

2.4 指令重排

在用MAC单元指令编程时,经常要改变MAC单元的特殊功能寄存器,比如IDX0,IDX1、QX0、QX1、QR0以及QR1等,在XC166单片机中,有一些指令将会阻塞在译码阶段,如果这些指令正好在一条修改特殊功能寄存器(SFR)指令之后执行,这种阻塞将引起3个机器周期的延时。

这些指令包括:

◇使用长地址模式的指令;

◇使用间接寻址的指令,除JMPS和CALLI外;

◇所有MAC单元指令(CoXXX指令)。

为了避免指令阻塞,在使用上述指令时,如有阻塞情况发生,应该重新重排指令,以消除延时,例如:

3 结论

用于英飞凌XC166单片机的DSP优化技术分为两类:与硬件相关的优化技术和独立于硬件的优化技术。独立于硬件的优化技术也可以用于其他的单片机或专用数字信号处理器。

程序 优化 方法 DSP 单片机 硬件技术 XC166 独立 相关文章:

- VxWorks实时操作系统下MPC8260ATM驱动的实现(11-11)

- Linux内核解读入门(11-09)

- Linux操作系统网络驱动程序编写(04-11)

- Linux系统对ISA总线DMA的实现(06-19)

- 基于MPEG-4的嵌入式多媒体监控系统中压缩/解压卡的设计与实现(10-15)

- Windows CE下驱动程序开发基础(04-10)