高效FIR滤波器的设计与仿真-基于FPGA

摘要:该文在介绍有限冲激响应(FIR)数字滤波器理论及常见实现方法的基础上,提出了一种基于FPGA的高效实现方案。该方案采用对称结构、加法和移位代替乘法运算、优化的CSD编码、流水线和级联技术等方面对传统的设计方法进行了改进,并借助FPGA滤波器芯片和Quartus II软件、Matlab软件对该方案进行了仿真验证。仿真实验结果表明:此种FIR滤波器的实现方法运算速度快、实时性好、节省硬件资源,其性能优于传统的FIR滤波器设计方法。

随着信息时代和数字世界的到来,数字信号处理已成为当今一门极其重要的学科。作为数字信号处理分支之一的数字滤波器,也受到了人们越来越多的关注。它是通信、语音、图像、自动控制、雷达、航空航天、医疗等领域中的一种基本处理部件,具有稳定性好、精度高、灵活性大等突出优点。

数字滤波器包括有限冲激响应(Finite impulse response,简称FIR)滤波器和无限冲激响应(Infinite impulse response,简称IIR)滤波器两大类,其中的FIR滤波器因可以得到严格的线性相位、有限精度的计算不会产生振荡、运算速度快等优点受到了人们更多的青睐。在非实时或低速系统中,FIR算法可以在DSP或CPU上用软件实现,但是在一些实时性要求较高的系统(如雷达控制、无线通讯系统等)中,由于受到乘法器和加法器电路的限制,该实现方法则不能满足速度的要求。近几年来,随着微电子技术与工艺的迅猛发展,现场可编程门阵列(Field programmable gate array,简称FPGA)以其可编程性、低成本性、高逻辑密度和高可靠性,得到了越来越广泛的应用。本文借助Ahera公司的FPGA芯片和Quartus II软件、Matlab软件,介绍了一种高效FIR滤波器的设计与实现方案。

1 基于FPGA的高效FIR滤波器的设计思路

一个Ⅳ阶的FIR数字滤波器可由差分方程

或转移函数:

来描述。式中: x(n)是滤波器的输入信号,y(n)是滤波器的输出信号,h(n)是滤波器系数。从以上的表达形式可以看出,FIR滤波器是通过加法器、移位器和乘法器组合而实现的,乘法器和加法器的效率及速度等特性对整个滤波器的性能起着决定性的作用。

1.1 采用对称结构

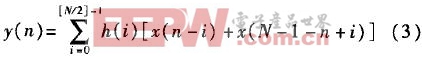

在很多应用场合,滤波器都是线性时间不变量(Linear time-invariant,简称LTI)滤波器,也就是带有常系数的滤波器。对于具有线性相位的FIR滤波器,其输出表达式(1)变成了如下的形式:

由此可见,利用它的对称形式比直接实现少用了一倍的乘法器,大大节省了硬件资源,而且可以提高速度。

1.2 用加法和移位代替乘法运算

乘法器是FIR滤波器中比较重要的部件,它的结构直接影响了滤波器的性能。传统的滤波器中的乘法器采用BOOTH乘法器结构,它主要

包括3个模块:BOOTH编码、部分积加法器阵列及进位加法器。在这种结构中,随着滤波器的阶数的增加,电路的规模势必迅速增加。

因为在实际应用的大多数情况下,滤波器的系数是固定的值,所以滤波器中所有的乘法都是固定系数乘法。实现固定系数乘法的一种常用方法是用移位和加法运算来代替并行乘法。这样一方面可以提高硬件实现的速度,另一方面可以减少所需的硬件资源。

1.3 采用优化的CSD编码

众所周知,二进制数在实现乘法或加法时,数值为0的位是不参与运算的。因此,对输入信号进行编码时,如果能使0位的数量最多,则完成相应的运算所需要的硬件将会大大减少,运算的速度也会相应地提高很多。正则有符号数字量(Canonic signed digit,简称CSD)正是基于此思想而提出来的一种新型编码方法,它是具有最少非0元素的表示法。

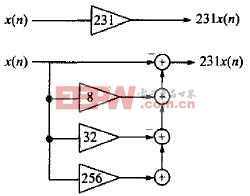

CSD码的特性是最终表达式在两个数位之间至少有一个0。它的算法是从最低有效位开始,用10…01取代所有大于2的一序列,用1101

取代1011;然后从最高有效位开始,用011代替101。例如十进制数231的CSD码为100101001,可以看出,在实现其乘法时,只需要4个加法器(如图1所示)。若采用普通的二进制代码实现,因(231)10=(11100111)2,需要5个加法器。可见,采用CSD码节省了加法器的数量。

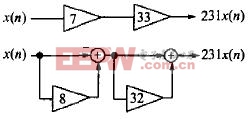

为了进一步提高效率,对于某些数据,还可以采用优化的CSD编码,即首先将系数拆分成几个因子,再实现每一个因子。如对231,首先拆分成7×33,然后分别实现因子7和33。7和33每个因子都只需要1个加法器(如图2所示),即实现231的乘法时只需要2个加法器,因此效率得到了更大的提高。

图1 231的CSD码的实现

图2 231的优化CSD码的实现

1.4 采用流水线技术

在滤波器的加法运算中,根据内部的数据流规则,可以采用流水线技术将一个运算操作分解成一些小规模的基本操作,将进位和中间值存储在寄存器中,并在下一个时钟周期内继续运算。对于FPGA器件来说,采用流水线式的设计,可以在不增加电路成本和规模的基础上提高运算处理的实时性。

1.5 采用级联技术

设计高阶的滤波器时,可以采用多个低阶滤波器级联而成,如n个10阶的FIR滤波器可以级联成一个10n阶的滤波器,级联后的滤波器可以

是对称的,也可以是非对称的。实践证明,采用分布式算法,级联后的滤波器不会因为长度的增加而使性能明显下降。

- Linux + Firefox 登陆网上银行(04-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- FIR数字滤波器分布式算法的原理及FPGA实现(08-07)

- 基于DSP Builder的FIR滤波器的设计与实现(08-04)

- 用DSP实现FIR数字滤波器 (06-04)

- 基于FPGA的FIR数字滤波器设计与仿真 (06-27)