高效FIR滤波器的设计与仿真-基于FPGA

2 高效FIR滤波器的FPGA实现

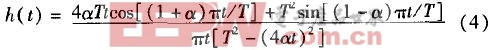

在实际的数字传输系统中,接收端和发送端为了达到最小的误码率,一般采用平方根升余弦滤波器。该滤波器的系统函数是:

式中:α是滚降系数,0≤α≤1,T为码元周期。

若取滚降系数α=1,滤波器长度为31,每个码元取4个样点,滤波器的系数采用10位量化,则可得到平方根升余弦滤波器的系数为h(n)=

{4,7,2,-7,9,4,22,25,-3,-53,-83,-43,88,277,445,512,445,277,88,-43,-83,-53,-3,25,22,4,-9,-7,2,7,4}。

根据以上思路,采用Altera公司Cyclone系列的EP1C3T100C6芯片,在Quartuas II开发软件下对此FIR滤波器进行设计及仿真。首先利用

VHDL语言完成设计输入,然后用Compiler进行编译调试。编译通过后,再利用该软件所提供的Waveform Editor进行时序仿真,得到的时序仿真波形如图3所示。其中,cP是控制输入的时钟信号,时钟频率为50 MHz,clr是加法器及锁存器的清零信号,低电平0有效,X是外部的输入信号,Y是最终的外部输出信号。

图3 FIR滤波器时序仿真图

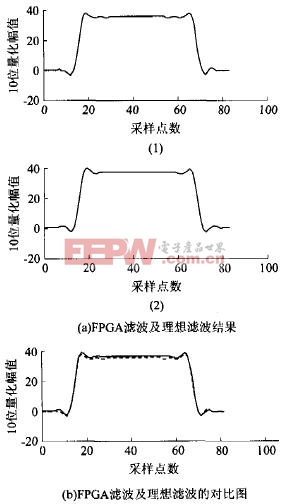

用Waveform Editor仿真后,将生成的波形转化为tbl文件,提取出波形数据。通过Matlab软件可以画出这些数据对应的图形,即滤波结果图,如图4中的虚线所示,图中横坐标是采样点数,纵坐标代表的是采用10位二进制数量化后的幅值,图4中的实线是FPGA滤波结果。从图4可以看出.用本文提出的设计方案实现的基于FPGA的FIR滤波器的滤波结果与理想滤波结果是非常接近的,对比图中FPGA滤波结果比理想值稍低,原因是由于在FPGA滤波器实现的过程中,为了节省硬件资源,将数据做了截掉低6位的处理,从而产生了一点误差。但是,从仿真结果来看,该截掉低位的处理并不影响滤波器的性能。

图4 FPGA仿真滤波结果与理想FIR滤波结果对比图

利用软件所提供的Timing Analyzer进行时间分析,可知此FIR设计方案的信号输出延迟在6.8 ns左右。即系统的最高工作频率为147 MHz。

从仿真结果中还可得到硬件资源的占用情况及利用率情况,实现该FIR滤波器共占用961个逻辑单元,逻辑单元利用率为33% 。

由以上分析可以看出,该设计方案不管是在速度及实时性方面还是在资源利用率上,都具有很大的优势。将其应用至通信系统或信号处理领域中均可满足实际的需要。

3 结论

FIR滤波器在数字信号处理的各个领域中起着举足轻重的作用,它的性能优劣对信号处理的结果有很大的影响。本文采用对称结构、加法和移位代替乘法运算、优化的CSD编码、流水线技术、级联技术几个方面,对传统的FIR滤波器的设计进行了改进,并借助Altera公司的FPGA芯片和Quartuas II软件以及Matlab软件对设计方案进行了仿真验证。仿真实验结果表明,该FIR滤波器的实现方案,具有工作速度快、实时信号好、节省硬件资源等特点,能够满足实际的数字系统的要求,应用方便。

- Linux + Firefox 登陆网上银行(04-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- FIR数字滤波器分布式算法的原理及FPGA实现(08-07)

- 基于DSP Builder的FIR滤波器的设计与实现(08-04)

- 用DSP实现FIR数字滤波器 (06-04)

- 基于FPGA的FIR数字滤波器设计与仿真 (06-27)