利用EP1C6Q240C8处理器的LCD滚屏设计

摘要:NIOSII嵌入式处理器以其设计灵活在嵌入式领域中得到广泛应用。文章以T6963C控制的240×128 LCD液晶显示屏模块阐述了一种基于EP1C6Q240C8处理器的液晶显示屏的滚屏显示的软硬件控制方法,并给出硬件原理图与部分软件代码。本方案对于NIOSII系统其他模块的开发具有借鉴意义。

关键词:液晶显示器;NiosII;可编程片上系统

0 引言

Nios II系列软核处理器是Altera的第二代FPGA嵌入式处理器,其性能超过200DMIPS,Altera的Stratix、Stratix GX、Stratix II和Cyclone系列FPGA全面支持Nios II处理器。Nios II系列包括3种产品:Nios II/f(快速)——最高的系统性能,中等FPGA使用量;NiosII/s(标准)——高性能,低FPGA使用量;Nios II/e(经济)——低性能,最低的FPGA使用量。这3种产品具有32位处理器的基本结构单元——32位指令大小,32位数据和地址路径,32位通用寄存器和32个外部中断源;使用同样的指令集架构(ISA),100%二进制代码兼容,设计者可以根据系统需求的变化更改CPU,选择满足性能和成本的最佳方案,而不会影响已有的软件投入。另外,Nios II系列支持60多个外设选项,开发者能够选择合适的外设,获得最合适的处理器、外设和接口组合,而不必支付根本不使用的硅片功能。本文采用CvcloneTM器件中的EP1C6Q24 0C8来实现雷达仿真电路显示模块的设计。

1 硬件设计

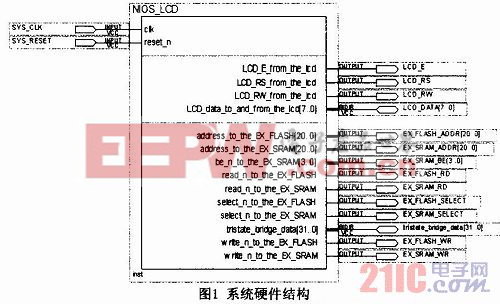

本系统的硬件设计结构如图1所示,主要包括以下部分:

1.1 EP1C6Q240C8及其配置芯片

本文系统中的处理器选用的是采用AItera公司提供的Cyclone系列的EP1C6Q240C8,该芯片采用240脚的PQFP封装,提供185个IO接口。

该芯片拥有5980个LEs;可提供92160bit的ram;芯片内部还自带有2个锁相环,可以在高速运行的时候保证系统时钟信号的稳定性。

在Nios II的硬件电路,通常使用Altera串行配置器件来存储FPGA配置文件*.Sof。

Altera串行配置器件可提供在系统编程(ISP)和多次编程能力,能够使FPGA和配置器件能够以最低的价格实现完整的可编程芯片系统(SO PC)解决方案。标准型配置器件,包括EPC2、EPC1、EPC1441、EPC1213、EPC1064和EPC1064V。本文使用EPC2配置器件。使用时,首先使用下载电缆将计算机生成的FPGA配置文件+.Sof使用programmer烧入EPC2配置器件中,然后由EPC2配置器件控制配置时序对FPGA进行配置,一次烧写即可重复使用,编程完后可以脱离计算机工作。

1.2 存储模块

存储模块包括两部分:只读存储器和随机存储器。只读存储器用来存储用户程序和需要下载的文件。由于利用EP1C6Q240C8处理器的LCD滚屏设计是较为复杂的SOPC系统,用户程序和需要下载的文件较大,用EPCS来存储是不现实的。根据设计的具体要求选择存储容量为4Mbit的FLASH作为只读存储器,并可使用flashprogrammer将*.elf和需要下载的文件烧入FLASH中,并在系统加电后实现调用。

随机存储器(RAM)主要是为了存放可执行代码和程序中用到的变量。由于所采用的处理器中的ram的存储容量较小,根据本文中设计电路的要求,采用8M的外部sram。

1.3 显示模块

LCD显示模块是由控制器、行驱动器、列驱动器和液晶显示屏等器件构成的。其核心部件LCD控制器是SOPC,它一方面提供与微控制器(即NIOS处理器)的接口,一方面连接行/列驱动器。通过对SOPC编程来实现对lcd的操作控制。本文采用的接口可编程芯片是T6963C来控制单色点阵图形LCD。

T6963C是一种内置控制器的图形液晶显示模块,其面向显示存储器的引脚有8根数据线(D7~D0)、16根地址线(AD15~AD0)和4根控制线,最多能管理64kB大小的显示存储器。T6963C单屏可以达到640×128像素,双屏可以达到640×256像素。

2 软件开发

基于NIOS II处理器的雷达仿真电路显示模块的软件设计丰要是使用NIOS通过对LCD的控制器进行编程以达到对LCD进行显示控制来实现的,其软件实现方案主要包括以下几部分:

2.1 T6963C初始化

显示模块软件开发首先要对控制LCD的T6963C的寄存器进行初始化,设置LCD的特性。其初始化包括:

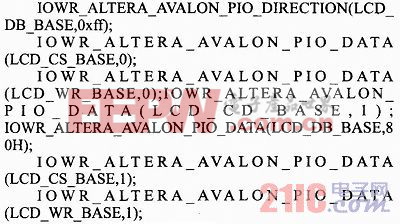

(1)设置文本和图形缓冲区的起始地址和宽度、屏幕每行的字节数。其软件设计主要依据表1指令来实现,部分软件代码如下所示:

(2)设置系统的字符和图形之间按“或”功能显示,其软件设计主要依据指令80H来实现,部分软件代码如下所示。

2.2 LCD滚屏设计

定时间、定间隔地修改文本显示区与图形显示区首地址将会产生显示画面滚动显示效果。软件实现如下,

图形显示区首地址的调整方法同文本区的调整方法相同。

3 结论

本文阐述基于NIOS II嵌入式处理器控制LCD的硬件设计方案和软件设计方法,充分体现了NIOS II嵌入式处理器在LCD设计中的灵活性。

设计 FPGA LCD 处理器 EP1C6Q240C8 利用 相关文章:

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)