FPGA上同步开关噪声的分析与解决方法介绍

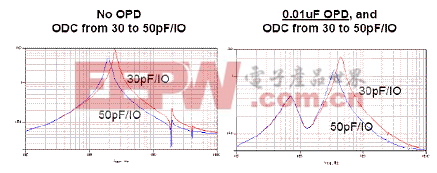

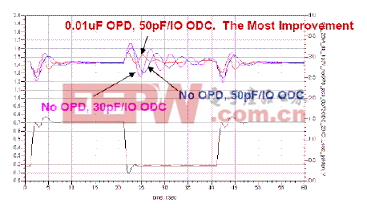

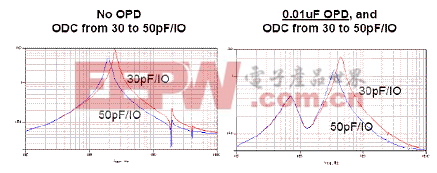

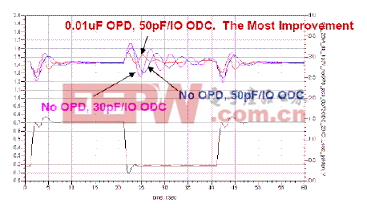

下图显示了电源网络的频域特性在不同电容作用下的仿真结果。初始的频域仿真可以看到电源网络阻抗在230Mhz 的频点附近达到最大值。随后的仿真显示了ODC(On DieCapacitance)和OPD(On Package Decoupling)的效果。其中OPD 作用在低频的范围,ODC 作用在较高频的范围。 时域仿真显示芯片内部电源的提高,这个结果也是符合实测的结果。 3. 封装和芯片中的去耦电容 下图显示了电源网络的频域特性在不同电容作用下的仿真结果。初始的频域仿真可以看到电源网络阻抗在230Mhz 的频点附近达到最大值。随后的仿真显示了ODC(On DieCapacitance)和OPD(On Package Decoupling)的效果。其中OPD 作用在低频的范围,ODC 作用在较高频的范围。 时域仿真显示芯片内部电源的提高,这个结果也是符合实测的结果。 可能的解决方法 1.可编程的电流强度 可以设置输出管脚的驱动电流强度值, 使用较小的电流值,会相应的降低SSN 噪声。这个方法要在保证信号完整性质量的情况的条件下使用。 2.可编程的信号斜率 Stratix IV的输出驱动可以可编程的输出斜率控制,这样可以配置低的噪声或者高速的性能。更快的斜率提供高速的翻转满足高性能的系统要求。慢的斜率有助于减少系统噪声,但是增加了一定的上升沿和下降沿的延迟。每一个输出管脚都有独立的边沿控制允许针对每一个输出定制斜率。 3. 可编程输出延迟 Stratix IV 器件在每一个单端输出驱动器也支持输出延迟。输出延迟链独立的控制每一个输出驱动器的上升沿和下降沿延迟。可以将同一个时钟沿翻转的管脚分成几组不同的延迟输出,有助于减少同步切换噪声。这个方法是在使用时序的余量来优化噪声。 4.合理的端接 合理的端接有利于减少反射,从而减少串扰的影响。Stratix IV器件的动态串行和并行端接可以提供阻抗匹配和端接能力。片内端接提供了比片外端接更好的信号质量,减少了寄生参数,同时减少板的面积也降低了成本。 5.软地和软电源 另外,未用的输入输出管脚散布在翻转的管脚之间,未用的管脚的状态会影响整体的SSN性能。把这些未用的管脚在单板上连接到平面或者电源平面有助于减少SSN 噪声。这种未用管脚的设计一般称为软地。

解决 方法 介绍 分析 噪声 同步 开关 FPGA 相关文章:

- SN2005学习系统 数字语音室解决方案(05-19)

- 以可编程DSP架构应对TD-SCDMA以及TD-LTE带来的设计挑战 (02-14)

- 基于DSP的电源解决方案(06-13)

- 间歇性Bug最佳解决方案(09-24)

- FPGA PCIe 视频采集(Video Capture)解决方案分析(06-06)

- 大联大友尚集团推出物体(人)感测应用解决方案(03-23)