间歇性Bug最佳解决方案

「间歇性」是代表不一定每次都会出现的状况,如间歇泉就是一个很好的例子。不同于一般的泉水会涌出大量的地下水,而是在特定的时间才会涌出泉水,然而研发产品时也会碰到这样子的状况,那就是间歇性Bug。间歇性Bug如同前面所叙述般,不是每次都会出现的问题,使得工程师们要解决这样子的Bug会较困难,想要分析间歇性Bug,单靠示波器是不够的,这时候就得需要逻辑分析仪。

逻辑分析仪在讯号撷取的方式不同于示波器,示波器可以Real time的方式撷取讯号,而逻辑分析仪则是将讯号储存于机器中再显示于屏幕上,再加上间歇性Bug并不是每次都会出现,所以逻辑分析仪的测量时间就变成一项重点。

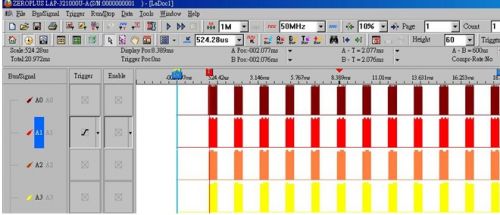

孕龙科技逻辑分析仪提供了业界唯一的专利功能"波形压缩"技术,这能够帮助始用者大大的增加仪器可测量的时间长度。以1M的内存、50MHz的取样率,在未开启压缩时的测量时间为20.972ms(如图一所示)

图一 : 未开启压缩

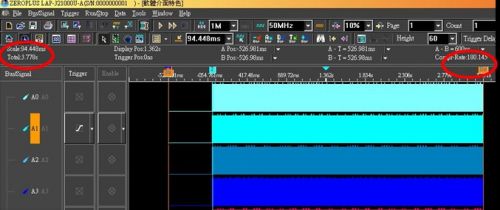

图二 : 已开启压缩

同样的内存及取样率,开启压缩功能后测量时间长度为3.778s,压缩率为180倍(如图二所示)如此就可以有效的将测量时间加长,可分析的数据相对也增加许多。

孕龙科技推出了更符合间歇性Bug的测量方案"限定子延迟技术",透过限定子延迟技术可以更准确的仅针对间歇性Bug发生时进行波形撷取。

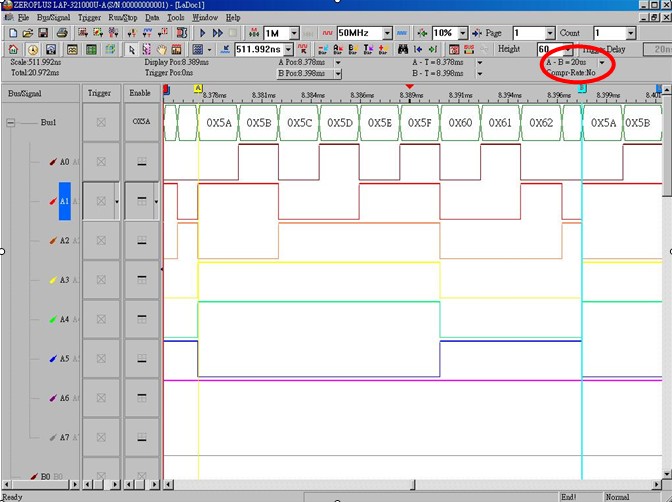

图三 : 使用限定子延迟

如图三所示,假设讯号的命令(Command)为5A,命令周期为20us,使用限定子延迟时可将5A设定为限定条件,而周期时间设定为延迟时间,如此LA运作时仅会撷取当5A成立后的20us。

另外孕龙科技还推出了「自动存盘」功能,工程师可以透过软件设定储存时间,当LA进行连续波形撷取时,软件会自动将撷取下来的波形自动进行存盘,以利工程师进行长时间讯号分析。(如图四所示)

图四 : 自动存档

- USB间歇性无法使用怎么办(12-12)

- TDD-嵌入C语言的测试驱动开发(05-19)

- EDM安全访问机制应用方案(02-12)

- 搞电子的女生眼中的电子世界是啥样的? (09-19)

- 第5章 动手操作-DEBUG的使用1(X86汇编教程)(12-01)

- 第6章 动手操作-DEBUG的使用2(X86汇编教程)(12-01)