可编程定时/计数器提高输出频率准确度方法

时钟源或多时钟源公倍数法。二时钟源公倍数法的具体做法是,将各输出频点分成两级,分别求出各组对应的公倍数fin1及fin2,若此fin1或fin2有一个大于脉冲发生器输入频率上限时,则重新分且,直到两组的公倍数fin1及fin2都达到输入频率上限要求。电路上设置相应的两振荡电压及二选一开关,根据输出频率而将对应的fin1或fin2切换到脉冲发生器的输入端。若分成两组后,无论怎样调整分组都不能使fin1及fin2同时满足输入频率上限要求,则可采用多时钟源公倍数法。考虑到增加时钟源数后,给软硬件带来的复杂性,在满足输入频率上限要求的前提下,时钟源数应尽量少。

(2)已知输出频率上限,不能确定具体期望输出频率时的情况

已知输出频率上限,不能确定具期望输出频率时,尽量提高fin或增加时钟源数,缩小近似子频段宽度,减小子频段内可能出现的max(|r|)及max(|Δf|)。

①提高时钟源fin法。若要求输出频率上限为fmax,则对应Nmin=fin/fmax=nmin+δ。输出频段可能出现的max(|r|)=1/(2nmin+1)若能使fin增大,则nmin增大,max(|r|)相应减小,从而提高了输出频率的准确度。

②多时钟源等分子频段法。提高时钟源fin,受脉冲发生器允许输入上限频率的制约,若还要提高输出频率准确度,可以增加时钟源数,将[fin/(nmin+1),fin/nmin]子频段作M等分,则可钭max(|r|)缩小M倍。

设有M个时钟源,其频率分别为fin,fin1,…,finM-1,可通过M选一开关,接入其一到脉冲发生器的输入端,经过nmin分频后,正好将[fin/(nmin+1),fin/nmin]M等分,即

fin1/nmin=fin/nmin-fin/[M·nmin(nmin+1)]

fin2/nmin=fin/nmin-2fin/[M·nmin(nmin+1)]

fin/nmin=fin/nmin-jfin/[M·nmin(nmin+1)]

finM-1/nmin=fin/nmin-(M-1)/[M·nmin(nmin+1)]

也即只要:finj=fin[1-j/[M(nmin+1)](j=1,2,…,M-1),就可以将子频段[fin/(nmin+1),fin/nmin]等分为M个子敬意。用量小|Δf|原则通过切换进相应的时钟源,f可以用fin/(nmin+1),finM-1/nmin,…,fin1/nmin,fin/nmin来近似。各子区间 max(|r|M)=(|r|)/M。一般地,当n>nmin时,M-1个增加的时钟finj(j=1,2,…,M-1),经n分频后不一定能将 [fin/(n+1),fin/n]作M部分,但能使此子频段分割,且各子区间宽度都小于fin/[M·nmin(nmin+1)],各子区间内的max (|r|)小于max(|r|m)。

3 实验结果

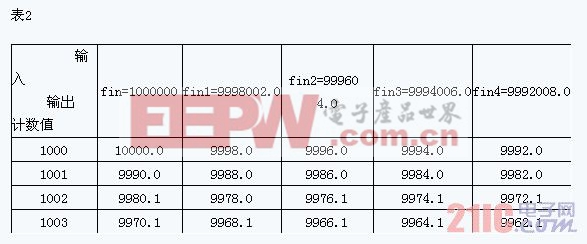

我们对多时钟源等分子频段法进行了实验,可编程定时/计数器采用Intel 8254-2,取fin=10MHz,fmax=10kHz,M=5,则nmin=1000,用频率计将各振荡器输出频率标定为:fin=10MHz,fin1=9 998 002.0Hz,fin2=9 996 004.0Hz,fin3=9 994 006.0Hz,fin4=9 992 008.0Hz。再将Intel 8254-2置入不同计数值,分别用各时钟源输入时,测出Intel 8254-2输出频率,结果如表2所列。

从表2可以看出,在单一时钟源时,计数器两相邻实际输出频率之差最大值为10.0Hz,输出频率准确度为±5.0 Hz,而在5时钟源时,计数器两相邻实际输出频率之差最大值为2.0Hz,输出频率准确度为±1.0Hz,输出频率准确度得到提高,为单时钟源时的5倍。

频率 准确度 方法 输出 提高 定时 计数器 可编程 相关文章:

- 基于DSP的高精度数字频率计的设计(02-03)

- 量身订制的DSP元件设计策略 (04-12)

- 基于DDS+PLL高性能频率合成器的设计与实现(04-24)

- 用DSP实现抖动(Jitter)测量的方法(04-28)

- 基于TMS320F2812的数字频率计的设计(05-11)

- 基于DSP的低频频率特性测试仪(03-06)