PDIUSBDl2芯片在USB接口电路中的应用

1 PDIUSBDl2芯片的性能与特点

Philps公司生产的型号为PDIUSBDl2的接口芯片是一个具有集成的SIE,FIFO存储器、发送器和电压调整器的高性能USB接口芯片,同时还支持DMA逻辑传输形式。他通常应用于基于微控制器的系统中,并且可以通过高速的并行接口和系统中的微处理器进行通信,其中最高并行接口速率可以达到2MB/s,是一个具有8位数据总线和一个地址的存储与数据交换设备。

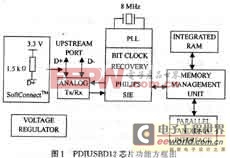

PDIUSBDl2芯片的功能方框图如图1所示。他采用28PIN脚模式,有S028和TSSOP28封装,SIE用来实现USB协议层的完整功能。具体功能如下:同步方式识别、并/串转换、比特填充/解填充、CRC校验/生成、PID确认/生成、地址识别和握手信号的鉴定/生成、批处理数据传输可达1 MB/s,3±0.3V双极性输入范围,可接受4.5~5.5V工作电压、工业级标准工作环境温度范围为一40~+85℃。也就是说,利用该芯片可以完成微控制器所送出的信号到符号USB规范的信号的转换。

|

2 USB工作电路

USB相对于其他传统接口而言,其快速数据传输能力和安装简单的和谐平衡在扫描仪上体现得尤为突出。传统的SCSI接口的扫描仪安装极为麻烦,并且对计算机的要求非常苛求,必须带有SCSI接口,并行接口传输数据又显得实在太慢。USB接口可以从速度和安装的简易性两方面满足用户的要求。现在的主流扫描仪生产厂家都在生产USB接口扫描仪,如HP,ACER和TARGA等公司都在纷纷推出,这种款式的机器具有以下的优点:

(1)USB接口可以有效地提升数据的传输速度。

(2)无外置电源设计,采用CIS技术,耗电量只有2W,便携可靠。

(3)采用了超薄超轻的设计,外观悦目。

2.1 硬件电路的设计

利用PDIUSBDl2集成电路来实现USB接口,可以允许设计者从市场上的多种微控制器中选择一种合适的产品来使用。这种灵活性可以通过使用现有的体系结构来降低开发费用,同时还可以缩短开发周期。

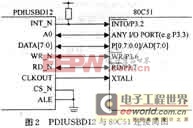

图2所示是采用了1个80C51的微控制器与PDIUSBDl2集成电路相互连接的简图。由于80C51是应用比较广泛的一种单片机微控制器,,软件开发工作者在其基础上开发大量的软件开发平台,大多数电子工程师对其的原因都比较熟悉。因此,用户可以利用比较熟悉的微处理器(80C51)进行核心程序的设计,即用80C51来实现其所需的功能,具体将数据信号转换为符合USB规则的信号,则完全由PDIUSBDl2来完成。这样以来,既可以利用80C51中丰富的软件资源,又可以利用USB总线技术的即插即用、热插拔等特性,可以使开发设备的成本降低、缩短开发产品的时间周期。

|

图3所示是利用PDIUSBDl2和1块80C51微处理器构成的硬件系统框图,他是将一个符合SCSI标准的扫描仪转换变成一个USB总线规范的设备,该方案对现有硬件进行最小改动的情况下达到了USB接口技术的实现。

|

2.2 数据信号驱动

USB使用一个差模驱动器来实现向USB电缆传输USB数据信号。在低输出状态,驱动器稳态输出的变化幅度必须是VOL<0.3V,此时应有1.5kΩ负载加到3.6V电源上;在高输出状态,驱动器稳态输出的变化幅度必须使Vho>2.8V,此时在地上有15kΩ负载,差模高输出状态和低输出状态之间输出的变化幅度必须很好地进行平衡,从而将信号偏差减至最小。另外,还需要驱动器上的摆动速率控制功能把辐射噪音和串话减至最小。驱动器输出必须支持三态操作,以此来进行双向半双工通信。同时还需高阻抗来将那些正在进行热插入操作或已经连接了但电源却没有接通的下行设备同端口隔离开来。相对于没有损坏的局部参考地而言,驱动器必须能承受信号管脚上的一o.5~3.8V电压。

2.3 数据信号接收

接受USB数据信号时也必须利用1个差模输入接受器。当2个差模数据输入以地电位作为参考,并且处于0.8-2.5V这样的范围之间时,接受器具有的灵敏度至少200mV,这称为共模输入电压范围。当差模信号线不在共模范围之内时,也要求能进行正确的数据接受。如果在没有损坏并以本地地电位作电位参考的条件下,接收器所能接收的稳态电平输入电压应该位于一o.5-3.8V之间。另外对于不同的接收器而言,每一条信号线都必须有1个单端接收器,这样接收器必须具有1个位于0。8~2.0V之间(TTL输入)这样的开关阀值电压。

3 USB接口工作电路主要参数

3.1 数据编码/解码

在传输信号时,USB应用了NRZI编码方式。在NRZI编码中,"1"由不出现电平变化来表示,而"0"由电平发生变化来表示。图4给出一个数据流和等同的NRZI码流,其中高电平代表数据线上的J状态,而图示代表了NRZI编码过程。一串"0"会使得NRZI数据每比特周期都会出现跳变,而一串连"1"则使得数据中长时间不会出现变化。

|

PDIUSBDl2 信号处理 USB接口 扫描仪 相关文章:

- 基于PDIUSBDl2芯片的USB接口设计(03-09)

- 用CPLD实现FIR数字滤波器的设计(08-07)

- 基于DSP的短波分集合成接收机(09-01)

- 数字信号处理器TMS320F241在变频空调中的应用(04-28)

- 什么是DSP及DSP技术详解(05-15)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)