基于DSP的GPS定位解算算法研究与实现

摘要:采用TI公司的TMS320C6713DSP芯片实现了GPS接收机定位解算功能。利用该芯片实现GPS接收机各模块的调度,完成对时间观测量和导航电文的提取,进行卫星位置解算和用户位置解算以及对外接口。试验结果表明,根据该方案设计的GPS接收机工程样机可以准确地实现定位解算功能。

关键词:GPS接收机;TMS320C6713;中断;EMIF;定位解算

0 引言

全球定位系统(GlobaI Positioning System,GPS)是一种全天候、全球覆盖、高精度的卫星导航定位系统。该系统向有适当接收设备的全球范围用户提供精确、连续的三维位置和时间信息。DSP芯片具有适合于数字信号处理的硬件和软件资源,运算速度快,精度高,接口丰富,稳定性好,可用于实现复杂的数字信号处理算法。随着DSP技术的发展,GPS卫星信号的实时处理越来越趋向于用DSP来实现。TMS320C67 13是TI公司生产的一种32位高性能浮点型数字信号处理器,功能强大,片内资源丰富,外扩存储器方便,运算速度快,无论从速度上还是精度上,TMS320C6713芯片都完全可以满足GPS接收机系统的设计要求。

1 GPS定位解算原理

1.1 用户位置的计算

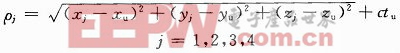

GPS卫星定位系统定位的基本原理是延时测距,通过测量空间己知位置上信号传播的时间延迟,确定该己知位置至用户的距离,根据测量距离解算出用户的三维位置和用户与已知位置的时间偏移量。为了确定用户的三维位置(xu,yu,zu)和时间偏移量,需要同时对4颗卫星进行跟踪并获取其伪距:

由于这个方程组是非线性的,很难直接求解,解非线性方程组一个常用的方法就是线性化。由于用户的三维位置和时间偏移量是未知量,于是可以认为未知的接收机位置和时间偏移量由近似分量 和修正分量△xu,△yu,△zu,△tu两部分组成,即:

和修正分量△xu,△yu,△zu,△tu两部分组成,即:

式中:ρj是第j颗卫星的伪距观测量;xj,yj,zj是根据第j颗卫星的星历计算出该颗卫星的位置,均为已知量;用户的三维位置和时间偏移量的修正分量△xu,△yu,△zu,△tu是未知量,近似分量 可以认为是已知量。因为可以给这些近似分量赋初值,由初值可以解出一组修正分量△xu,△yu,△zu,△tu,近似分量经过修正之后又可以认为是已知量,重复这个计算过程,直到修正分量小到预定的范围之内。最后的近似分量

可以认为是已知量。因为可以给这些近似分量赋初值,由初值可以解出一组修正分量△xu,△yu,△zu,△tu,近似分量经过修正之后又可以认为是已知量,重复这个计算过程,直到修正分量小到预定的范围之内。最后的近似分量 就是要解的用户的三维位置和时间偏移量。这种方法即基于线性化的迭代法。

就是要解的用户的三维位置和时间偏移量。这种方法即基于线性化的迭代法。

1.2 伪距的获取

分析GPS定位解算算法可知,要解算用户的三维位置和时间偏移量,首先需要获得各颗卫星的位置和相应的伪距观测量,因此,伪距观测量的精度直接影响到用户位置解算的精度。

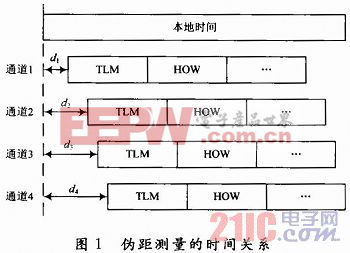

在GPS接收机中,可以任意选择一个时刻作为本地参考时间,本地参考时间与GPS系统时间的差值即为时间偏移量tu。对于GPS信号发射时间而言,如果不考虑每颗卫星的时钟修正项,所有卫星的导航电文子帧1的起始点都是在同一时刻发射的,因此可以认为不同卫星的导航电文子帧1的发射时刻是相同的,但是不同卫星的子帧1的起始点是在不同时刻接收到的,这个时间差就代表不同卫星到接收机的时间差,即距离差。在导航电文中,子帧1每30 s出现1次,而不同卫星信号到达接收机所需时间的差值最大只有20 ms。因此,很容易保证所观测的不同卫星的子帧1都是在同一时刻发送的。统计本地参考时间与所接收到的卫星星历子帧1的开始位置的时间间隔即可得到伪距信息,如图1所示为伪距测量的时间关系。

在GPS接收机内部存在两种时间统计方式,本地时间T和道时间Ti。本地时间可以选择任意一个时刻作为参考,之后便由本地晶振计数累加。通道时间由三部分组成:20 ms计数TD,1 ms计数TCA和C/A码相位计数TCAphasc。每个通道在接收到导航电文子帧1的TLM遥测字时刻,三个计数值同时清零,之后由跟踪得到的C/A码相位为步长累加,即通道时间Ti为:

Ti=TD/50+TCA/1 000+TCAphasc/(1 023×1 000)

在某一中断时刻,本地参考时间与GPS系统时间的差值即为时间偏移量tu,本地参考时问和各个通道时间的差值与光速乘积即为ρi,即:

ρi=(T-Ti)·c

2 系统方案设计

一般来说,在实时信号处理系统中,底层信号处理的特点是处理的数据量大,处理速度高,但运算结构相对比较简单,适于用FPGA进行硬件实现,这样能同时兼顾速度及灵活性。上层信号处理的特点是处理的数据量较少,但算法的控制结构复杂,适于用运算速度高,寻址方式灵活,通信机制丰富的DSP芯片来实现。

由于GPS接收机系统涉及到GPS信号捕获算法、载波跟踪算法、码跟踪算法、卫星位置解算,用户位置解算、以及大量的相关算法计算,综合算法复杂且运算量相当大,同时GPS接收机系统要求很高的定位精度和实时的动态性能,对系统的体积、功耗、稳定性等也都有较严格的要求。如果所有任务都由DSP来完成,不仅对DSP的压力很大,还有可能满足不了系统的实时性要求。为了协同DSP完成整个GPS接收机系统的工作,在该系统中采用一片DSP高速微处理器和FPGA大规模可编程阵列组合搭建了系统硬件平台,FPGA主要完成GPS信号的捕获、跟踪和解扩解调,以得到导航和测距信息;DSP芯片作为系统的主处理芯片,主要负责数据处理,以及对逻辑控制模块的通信与控制,而系统外围设备的控制与通信工作由FPGA完成。这样可以使整个系统的任务合理分配,DSP芯片能更专注于大量数据的处理,使信号处理的实时性得以保证。总体框图如2所示。

算法 研究 实现 解算 定位 DSP GPS 基于 相关文章:

- 用FPGA实现FFT算法(06-21)

- FIR数字滤波器分布式算法的原理及FPGA实现(08-07)

- 基于算法的DSP硬件结构分析(04-02)

- 基于DSP的音频会议信号合成算法研究(05-10)

- 基于DSP的Max-Log-MAP算法实现与优化(05-27)

- 一种长序列小波变换快速算法的DSP实现(08-11)