基于SAA6752HS 的嵌入式视频监控和传输系统的设计

GA实现SAA6752 与TMS320VC5502 之间的接口。如上SAA6752HS 与TMS320VC5502 的连接图4 所示,移位寄存器负责将SAA6752HS 输出的8 位数据方式扩展成32 位宽度,以提高数据的吞吐效率。通过时钟信号PDIOCLK、有效位信号PDOVAL 和音视频标志位PDOAV 来控制移位寄存器的工作。FIFO是一个宽度为32 位的缓冲器,TMS320VC5502 通过片选信号CE3 和读信号ARE/SRE/SDRE 控制对FIFO 数据的读操作。

当SAA6752HS 采用传送流的数据结构时,每读完4 个数据包(每个数据包为188个字节) , 计数器2 就会产生一次中断,TMS320VC5502 从FIFO 中读入这些数据包,完成信道编码后向网络上传输。FPGA 逻辑正是依据这一思想设计的。为了提升系统的稳定性,避免累积错误,该逻辑中采用了一种双FIFO 轮流切换的方法。在系统开始运行,只往FIFO1 里写,当写完4 个数据包,产生一次中断,通知DSP 来读数据;接下来,系统自动切换到往FIFO2 里写,此时DSP 同时在读FIFO1里的数据,直到往FIFO2 里写完4 个数据包(由于DSP 读数据的速度远远快于SAA6752 往FIFO 里写数据的速度,故此时FIFO1 已被读空) ,便又产生中断;接下来,DSP 读FIFO2 里的数据,同时往FIFO1里写,依次轮流切换。

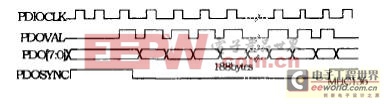

图7 DIO 主模式下输出传输流分组的时序图

SAA6752 的输出采用DIO 主模式,其输出端口的时序如图7 所示,每个数据包包含188 个字节,这是MPEG2 传输流分组的特性。在MAX+PLUSII 下设计其逻辑,运行正常。

结束语

本文针对数字视频压缩及网络传输作了较为深入的研究,并针对嵌入式网络视频服务器的设计和实现作了初步而有益的探索,其中既有经验也有教训。由于时间及其它因素的限制,研究工作留有许多需要完善的地方。Non-PCI 结构网络接口性能的优化和客户端软件的具体实现及形成嵌入式网络视频服务器原理样机是我们下一步的目标。

视频采集 MPEG2 以太网传输 SAA6752H 相关文章:

- 基于DSP的视频采集系统设计(08-02)

- 基于DSP的视频采集系统仿真设计(01-09)

- 基于TMS320DM642的视频采集驱动程序的实现(09-26)

- 基于Android平台的智能手持终端Camera模组驱动设计与研究(11-22)

- FPGA PCIe 视频采集(Video Capture)解决方案分析(06-06)

- 一种基于FPGA技术的红外视频采集系统设计(06-05)