基于SAA6752HS 的嵌入式视频监控和传输系统的设计

图4 SAA6752HS 与TMS320VC5502 的连接图

需要说明的是,图4 中的移位寄存器、FIFO、计数器(模4) ,计数器2 (模47) 是用FPGA 实现。DSP 控制器我们选用的是TI 公司中的TMS320VC5502(‘5502) 芯片,它的核心电压只有1.2V ,功耗仅0. 05mW/MIPs ,性能达600MIPS。这款芯片尤其适合于数据速率高,运算量大,又要求低功耗的系统。同时TMS320VC5502 集成了丰富外围设备,比如32 位的外部内存接口(EMIF) ,可以与系统中的网卡连接;内部集成的I2C 总线接口,便于对Philips 的视频芯片进行控制。另外,它还对外提供JTAG口,这使系统的调试可依靠JTAG仿真器和TI 公司最新的DSP 开发平台CCS 而变得更为方便。

视频流以太网传送子系统

以太网接口部分主要用来将打好包的数据传到远程主机上, 我们使用的是SMSC 公司的LAN91C111 芯片,它是一块高性能非PCI 接口的10M/100M以太网接口的芯片。LAN91C111 采用的是一种流量I/O 的工作方式。所谓流量IO 方式曾经是为磁盘与处理器接口而设计的,它比ISA 的DMA 方式具有更高的效能而且能更方便的使用。LAN91C111 对数据的处理能力也很强,其理论上最大数据处理能力为320Mbit/s = 40MB/s。由于LAN91C111 具有MMU 功能使得整个系统具有较高的网络性能和较低的系统开销。

图5 LAN91C111 的接口图

由 LAN91C111 组成的网络接口如图5 所示。LAN91C111 通过局部总线接口把CPU 传过来的数据,通过内部的MAC 控制器进行数据的封装,物理层收发器(PHY) 将数据传输到脉冲变压器上,这样由噪声产生的错误可以降至最低,保证数据的正确传输。同时,LAN91C111 的物理层收发器还能接收网络上的数据包,并且MAC 可以进行载波侦听、碰撞检测协议和CRC 校验功能;此外LAN91C111 还具有大的缓冲区可以提高整个电路的效率,LED控制器可以标识网络接口的状态。LAN91C111 的主机端的接口比较灵活,它可以支持异步或同步方式的传输,还可以支持非触发方式和触发方式(Burst mode) 的传输。为了提高系统的吞吐率,由DSP 向网卡传送数据时,通过DSP 的EMIF 接口,采用同步触发传输方式,并且使用直接32 位数据传输,数据不通过BIU ,直接写入网卡FIFO ,这样更为合理地实现TMS320VC5502 与LAN91C111 高速连接。

系统软件设计

本系统的软件包括两大部分,一是硬件驱动程序,二是控制逻辑设计。下面分而述之。

系统驱动程序设计

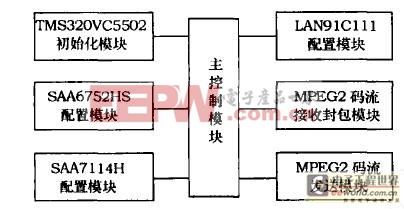

环境下进行的。CCS 界面简单明了,操作方便,功能强大,大大降低了开发的难度。系统的驱动程序由TMS320VC5502 初始化程序,SAA7114A ,SAA6752HS 和LAN91C111 的配置程序、数字视频MPEG2 码流接收存储封包程序、MPEG2 码流以太网发送程序和系统主控程序等多个模块组成。图6 为软件系统框图。

图6 软件系统框图

TMS32VC5502 的初始化程序完成对‘C5502 的堆栈和运行状态位,中断使能位的设置,以及DSP内核频率的设置。SAA7114 和SAA6752HS 的配置程序通过‘C5502 的I2C 接口完成对其的设置,使其能正常地进行模拟解码和数字编码。LAN91C111 的初始化程序完成对该芯片的一些寄存器设置,使其能正常运转起来。数字视频MPEG2 码流接收存储封包程序是通过‘C5502 将SAA6752HS 传过来的数据按照RTP 协议标准打成网络上的数据包,然后再通过MPEG2码流以太网发送程序将数据包发送出去。数据传输时都是使用的DMA 传输方式,这样可以节省大量的时间,提高系统运行的效率。

在整个驱动程序设计当中,时序的把握是十分关键的。比如SAA7114 的配置程序,当中需要用到I2C 总线,而I2C 总线对时序要求是相当严格的,如果在发出START 命令之后,不加上一定的时延,而立即传送数据,由于DSP 的速度太快,可能会造成前后数据的覆盖,导致程序出错。另外,由于系统是进行实时处理的,中断程序设计是必不可少的。在程序设计时有几个问题需要注意:

第一, 当外部中断信号不稳定时,比如波形前后跳动、毛刺过多等,都有可能造成能检测到中断,但无法进入中断服务程序的情况。

第二, 若将程序单步执行,这样会造成仿真器出错,无法检测到中断。

第三, 在修改两个中断矢量指针IVPD 和IVPH 之前,应确信:

a、禁止所有的可屏蔽中断( INTM= 1) 。这可以在修改中断矢量指针,使之指向新中断矢量之前,防止产生一个可屏蔽中断。

b、每个硬件非屏蔽中断对新旧IVPD 值分别有一个中断矢量和一个中断服务程序。这样在修改IVPD 过程中,产生一个硬件非屏蔽中断时,可以防止非法指令代码。

FPGA 逻辑设计

该系统中使用了一块Altera 公司的ACEXEP1K30QC208-3Q 型号的FPGA ,主要利用该FP

视频采集 MPEG2 以太网传输 SAA6752H 相关文章:

- 基于DSP的视频采集系统设计(08-02)

- 基于DSP的视频采集系统仿真设计(01-09)

- 基于TMS320DM642的视频采集驱动程序的实现(09-26)

- 基于Android平台的智能手持终端Camera模组驱动设计与研究(11-22)

- FPGA PCIe 视频采集(Video Capture)解决方案分析(06-06)

- 一种基于FPGA技术的红外视频采集系统设计(06-05)