一个嵌入式视频监控系统的设计与实现

引言

传统的数字视频监控多采用数字芯片集成或采用纯PC监控,由于数字芯片无智能化的操作系统而PC机处理多路视频信号的速度较低,导致系统稳定性不够好。随着嵌入式系统和视频压缩技术的日渐成熟,以及高网络带宽的普及,通过嵌入式平台,将视频信号数字化并压缩,并通过内置的Web服务提供给访问者已成为可能。用户可在现有网络环境中,通过浏览器直接观看实时的监控图像,实现高效、简洁的监控操作。以嵌入式系统为基础的数字视频监控具有:便于计算机处理,适合远距离传输,可靠性高、安装方便、使用灵活和体积轻巧等优点[1- 3]。

1 系统组成方案

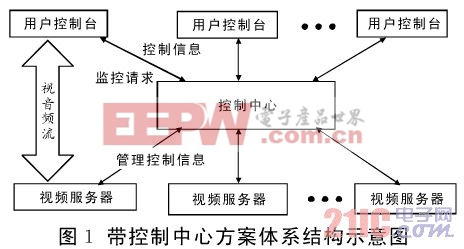

我们设计的嵌入式视频监控系统由视频服务器、控制中心、和客户端组成,这是因为当监控点和控制台到达一定数目之后,监控点对于用户的开销也越来越大,因此增加控制中心辅助进行管理。系统结构如图1所示。

1) 嵌入式视频服务器

嵌入式的视频服务器由硬件模块和软件模块组成。视频服务器硬件模块主要完成视频信号采集、压缩、网络传输和用户设置,每个视频服务器出厂时被分配了一个唯一的序列号作为用户访问的唯一标识。嵌入式软件模块的主要功能有是控制硬件和向用户传输经过压缩的视音频数据。

2) 控制中心

控制中心主要处理从客户端发送过来的视频监控信息,然后将许可的请求通知视频服务器,使它们之间建立有效连接以传输监控视频数据;另外,控制中心负责视频服务器的登记注册,设定用户权限和视频服务器的参数。控制中心软件运行在PC服务器上,由管理员操作维护。

3) 客户端

客户端是提供给用户使用的基于PC的操作界面,可根据不同用户权限设定其操作功能。客户端完成控制中心的管理维护、图像观看、云台调整、图像参数调整、录像、告警等功能。

2 视频终端硬件设计

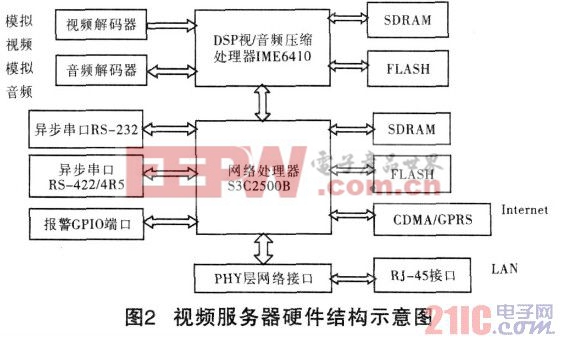

视频终端硬件完成视频信号采集、MPEG-4压缩和网络传输。由于高精度实时视频信息量巨大,在传输时需丢弃大量数据帧,因此必须压缩[4]。我们采用专用芯片按即定格式高速压缩视频,实时性好,可靠性高。系统视频服务器硬件的结构如图2所示。

(1) 视频解码器模块:采用SAA7114H视频解码芯片,主要功能是将1路模拟视频量化后形成YUV数据格式通过并行输出端口传输到IME6410视频MPEG-4压缩处理单元。

(2) 音频编解码器模块:主要是完成模拟音频到数字音频的解码工作,采样速率32K bps。

(3) MPEG-4压缩处理器模块:数字视频数据编码压缩工作由INTIME公司设计的IME6410视/音频压缩处理器完成。微控制器通过主机接口对IME6410配置和接收压缩得到的视频码流。

(4) SDRAM模块:IME6410和网络处理器S3C2500B各需要一片SDRAM,为DSP和网络处理器中程序运行提供外部存储器。

(5) FLASH模块:用来存储DSP和网络处理器中运行的程序。

(6) 网络处理器模块:选用SAMSUNG的ARM940T内核的S3C2500B网络处理器,S3C2500B将编码后的视频/音频数据流打包形成标准的网络数据流并传输到因特网中。用户可通过互联网发送命令,对IP编码器进行参数调整,例如编码的帧率、编码效率、图像质量、IP地址设定等。

(7) 异步串口:支持RS-232、RS-422/485等多种协议,用于和PC通讯和控制摄像头。用户可根据需要设置系统的工作参数,例如网络的IP地址,编码的帧率、编码效率、图像质量等。

(8) I/O模块:通用I/O接口可以满足用户的控制目的,例如摄像机的镜头焦距控制等。

(9) PHY层网络接口:完成调制、解调功能。

3 嵌入式视频服务器软件的设计与实现

uCLinux具有精巧、高效的内核,完整的网络功能和良好的可裁剪性,它内置的TCP/IP协议找、良好的开放性和可扩展性以及高效的任务管理,能够满足数字视频服务器的要求[5]。

本视频服务器采用了uCLinux作为嵌入式操作系统,移植BLOB作为系统引导模块,移植ez-ipupdate实现动态域名解析,使用在系统内核态下编写的driver实现视频数据的获取,使用在系统用户态下编写的应用服务程序iplay实现组帧、发送以及与用户交互等功能。

3.1 系统引导模块

系统引导模块LOADER移植自BLOB(Boot Loader OBject)项目,它是LART项目的系统引导模块。移植的BLOB的发行版是BLOB-2.0.5-pre2,编译器使用arm-linux- toolchain。由于视频服务器上的硬件环境与处理器SAMAUNG的S3C2500B的软件开发包SMDK2500中的配置有所不同,因此对 BLOB中的源代码在移植过程中作出了修改。以下是对BLOB程序做出的具体修改。

(1) 串口参数代码修改

由于视频服务器上的串口时钟源和SMDK2500不一样,因此对文件“/src/lib/serial-s3c2500.c”做出修改。

(2) 修改BLOB程序中各块在内存中的分布。

因为

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)