基于单片机和可编程逻辑器件的LED显示屏显示

-D为双3-8译码器构成的4-16译码器的数据输入,实现显示行选通控制; sdr为红数据信号线;sdb为绿数据信号线。

其工作过程为:S3状态,sck脉冲置0,sdr和sdb分别输出一位数据;S4状态时,sck置 1,红和绿数据分别移入相应移位寄存器BMI5026,若不足8位时,返回S3状态,若不足一行时,返回S1状态,读下一个字节,若完成一行数据移位过程,则转S5状态;S5状态时,置le为0,将BMI5026的缓冲寄存中一个显示行的点阵数据送输出寄存器,同时置cs1有效,控制第hcnt行的点阵显示,然后判断一屏内容是否显示完成,返回s1状态。图4为完整的有限状态机的状态图。

下面给出LED显示屏体驱动时序信号对应的Verilog HDL程序代码:

s3: begin

sck=1'b0;

sdr= SDA color[0];

sdb= SDC color[1];

OE=1'b1; CE=1'b1;

state=s4;

end

s4: begin // 移位输出到LED显示屏

sck = 1'b1;

shcnt = shcnt +1'b1;

if (shcnt = = 0)

begin

addr=addr+1'b1; //读完一个字节地址记数器加1

byte=byte+8'b1;

if(byte= = nrow)// 如果读完一行数据

begin

oe1=1'b1;//关LED显示

cs=1'b1;

le=1'b0;//驱动芯片写入数据

byte = 8'b0;

state=s5;//读完一行数据则显示

end

else state=s1;

end

else state=s3; //当前字节移位输出

end

s5: begin

sck=1'b0;

le=1'b0;

counter=hcnt;

OE=1'b1;

CE=1'b0;

if(addr = = nscreen)

addr=0;

oe1=1'b0;

cs=1'b0;

state =s1;

end

4系统测试及仿真

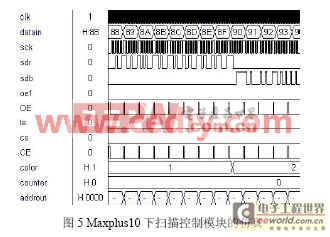

系统的开发调试环境是:单片机部分在KeilC51下调试,CPLD部分在Maxplus10下调试。LED显示屏的扫描控制模块的Verilog HDL源程序编写完成后,在ALTERA公司Maxplus10可以先进行软件仿真,以观察各信号是否符合硬件电路所需的时序要求。图5为扫描模块 CLPD仿真结果,符合设计要求。通过JTAG接口下载到ATF1508AS后,系统工作正常。

5 结束语

基于Verilog HDL实现的LED显示屏扫描控制模块,应用于我们开发LED大屏幕电子信息显示屏系统,简化了系统结构,提高性了性价比。该LED显示屏在实际应用中具有良好的显示效果,画面清晰、性能稳定,已经在学校的多个部门得到应用。

LED 显示屏 显示 器件 逻辑 单片机 可编程 基于 相关文章:

- DSP在LED大屏显示中的应用(03-14)

- DSP在LED显示中的应用(08-21)

- 基于μC/OS2II的LED显示屏控制器(08-14)

- 基于DSP的LED大屏幕显示系统(10-03)

- 基于单片机的彩灯设计方案(10-29)

- 基于μC/OS-II及Nios II的多窗口显示屏控制器的设计与实现(01-23)