基于ARM的智能来电显示器的设计

摘要:介绍基于ARM的来电号码显示器的实现方法。利用CID芯片HT9032C来解调FSK码,同时可实现液晶显示、E2PROM存储和语音播报电话主叫号码等功能,以SPI串行接口智能显示键盘控制芯片ZLG7289A为核心设计的键盘电路可实现查阅、删除信息。文章详细介绍了系统的硬件电路设计和软件流程。实践表明,显示器外围器件少,抗干扰能力强,使用方便。

0引言

目前我国电话网交换机传送主叫识别信息CID(CallingIdentityDelivery)有两种方式,较常用的是FSK(频移键控)方式,另一种是DTMF(双音多频)方式。通过掌握相应的协议标准和数据格式,可通过ARM控制芯片HT9032C实现解调FSK格式的来电信息,通过E2PROM存储器存储来电信息,并利用液晶显示,同时控制ISD1402语音芯片播放来电号码。以SPI串行接口智能显示键盘控制芯片ZLG7289A为核心设计的键盘电路实现查阅、删除来电信息。

1系统硬件设计

1。1系统总体设计

整个系统由5部分组成,分别是:(1)FSK信号解调;(2)来电号码语音播报;(3)显示来电;(4)存储来电信息;(5)按键控制部分。具体如图1所示。

图1系统组成框图

1。2系统各组成部分设计

(1)FSK信号解调。

CID芯片HT9032C解调器是台湾HOLTEK公司生产的双列直插、低功耗的接收物理层主叫识别信息的CMOS集成电路FSK解调芯片,它能满足Bell202和CCITTV。23标准,实现1200波特率FSK数据传输标准,且能检测铃流和载波,电话线经过接口电路接到HT9032C的TIP,RING,RDET1和RDET2脚,当有振铃信号来时,HT9032C的RDET脚触发下降沿。在第一次和第二次振铃之间HT9032C把逻辑1(1200±12)Hz、逻辑0(2200±22)Hz、传输速率为1200bit/s的FSK信号解调成串行异步二进制数据。当检测到有效载波信号,CDET触发下降沿。在DOUT脚输出包括信道占用信号、标志信号和主叫识别信号的所有信号;在DOUTC脚只输出主叫识别信号。

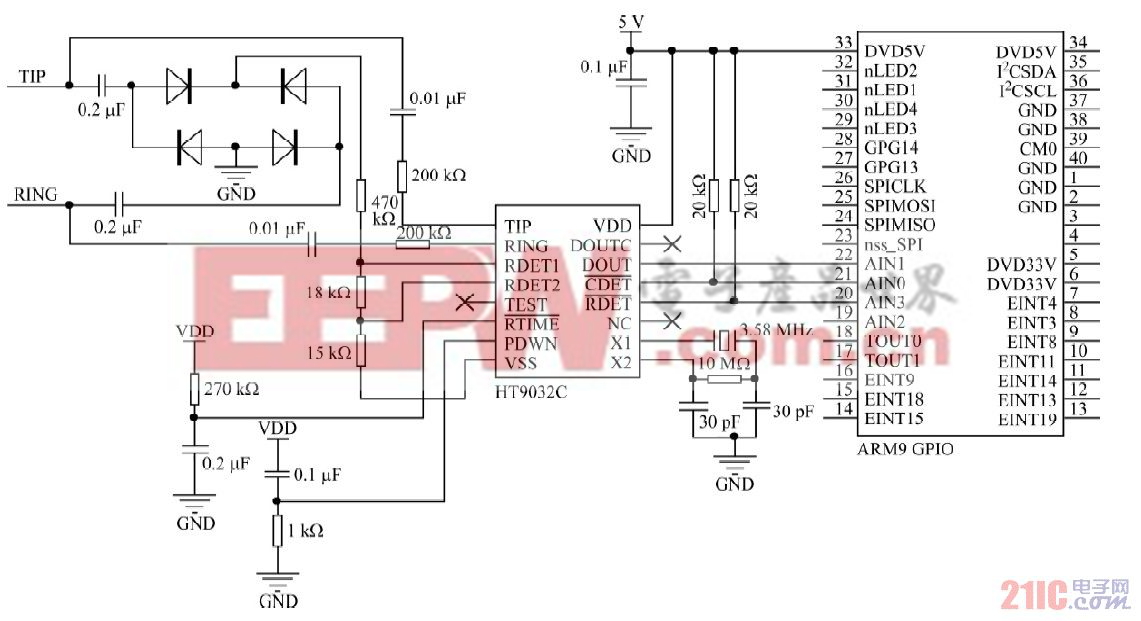

HT9032C与ARM9的具体硬件连线如图2所示。

图2CID芯片HT9032C与ARM9的硬件连线

HT9032C的RDET引脚接MCU的外部中断0,当有振铃信号时,RDET脚触发外部中断0服务程序。

HT9032C的CDET引脚接MCU的外部中断1,当检测到有效解调后的主叫识别信号,CDET脚触发外部中断1程序。HT9032C的DOUTC引脚接MCU的串行中断。当检测到振铃和有效载波信号,便打开串口中断,接收解调的FSK信号,得到来电信息。

(2)来电号码语音播报。

采用录放一体化的高保真单片固态语音集成电路ISD1420实现自动语音播放来电号码。其内部有128K的E2PROM用于存放语音信息,并可分成160段,每段信息为0。125s,总共可存储20s的信息。语音分段的信息是由ISD1420的地址线A0~A7的值决定的。在录制过程中将可能要播放的语音库按每个0。5s的单位进行录制,每个汉字或数字的语音信息对应到一个地址。在检测到来电号码后,依次给定A0~A7的值就能构成一句话,播放来电号码。

(3)显示来电。

液晶显示模块LCD用来显示主叫号码、日期、时间等信息。LCD接收到来电信息后即依次取出各个信息并进行显示。

(4)存储来电信息。

采用允许三总线工作的串行外设接口(SPI)芯片X25045作为存储器。此芯片把看门狗定时器、电压监控和E2PROM集成在单个封装内,降低了系统成本并减少了对电路板空间的要求;其看门狗功能提供了对微控制器的保护,通过编程监控系统,当系统发生故障时自动以RESET信号作出响应;X25045的存贮器部分是CMOS的4096bit(512×8)串行E2PROM。

(5)按键控制部分。

采用ZLG7289A控制3个按键:DEL、上UP、下DOWN分别用于删除、查阅主叫信息。

2主叫识别信息的两种数据格式

终端交换机向该被叫用户传送主叫识别信息数据传送时序如图3所示。

图3主叫识别信息数据传送时序

符号时间值:

A-0。5~1。5s第一次振铃结束与数据传送开始之间的时间间隔。

B+C-2。9s传送数据的时间包括信道占用信号ChannelSeizureSignal和标志信号MarkSignal。

D-0。2s数据传送结束与第二次振铃开始之间的时间隔。

E-1s铃流。

B+C+D-3。1s各时段可根据具体情况定。

信道占用信号和标志信号的目的是提示电话终端准备接收数据,校验字是用作差错检查。信道占用信号是由一组300个连续的0和1交替的位组成,其第一个比特为0,最后一个比特为1。在通话状态下,信道占用信号不发送。标志信号是由180个(在挂机状态下)或80个(在通话状态下)标志位(逻辑1)组成,标志位由0~10个逻辑1组成。

每个数据字之前先行一位0作为起始位,在最后加一位1作为结束位,每个数据字的最低位先发送。这样,实际每个字占10bit,即1PXXXXXXX0(P为奇偶校

- 基于DSP Builder的VGA接口系统设计(04-10)

- 基于DSP的液晶显示器接口设计及控制实现(10-15)

- DIY小设计:智能闹钟的简单软硬件实现(04-14)

- 基于PIC32单片机的新型LED点阵显示控制系统设计(10-01)

- 通过虚拟现实对装甲越野车辆进行仿真和测试(12-31)

- 藏在系统核心芯片中的DRAM控制器(12-10)