嵌入式系统应用中NV SRAM存储器的应用

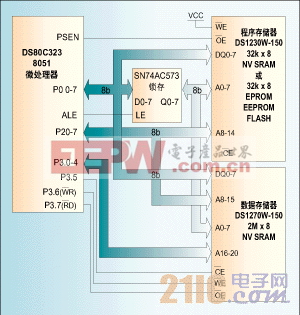

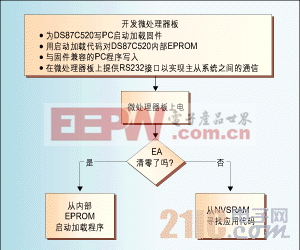

程序存储器输出使能控制,8051的RD信号(P3。7)用于数据存储器的输出使能控制。当两个存储器输出同时驱动到总线时,会导致总线冲突;另一种出现总线冲突的可能是微控制器将数据输送给NVSRAM的时候,外部存储器受指令控制输出数据。这些情况都需要在设计中慎重考虑,以避免总线冲突。 针对这种设计需要说明两点:首先,程序存储器必须始终加写保护;其次,数据存储器的可寻址空间可能大于微处理器寻址空间。 当NVSRAM的WE引脚置为高电平时,不能写入任何数据,因此,需利用存储器编程器对该引脚进行编程。BPMicrosystems和DataI/O编程器几乎支持所有Dallas半导体的NV SRAM。当采用编程器进行器件编程时,注意在把器件安装到电路之前要避免器件受ESD冲击,因为ESD冲击会造成器件中的数据丢失。一旦器件在保证数据正确的前提下装入线路板,NVSRAM将有效保证数据的完整性。 如果需要寻址更多的数据存储器,只需在微处理器的数字接口简单地添加高位地址线即可,图中所示的8051支持64kB(A0-A15)的寻址空间,最高5位地址线(A16-20)和片选引脚可用于选择64kB存储器页,对于编程器而言采取读、写子程序能使大容量存储变得完全透明。上述操作不适用于程序存储器,由于微处理器取代码时不允许页选择,它按照16位地址取指令,可能选择错误的页码。如果图1选用DS1245,则只能寻址到一半的数据。如果用A16建立第二页存储器,当存取第二页的数据时会导致微控制器取第二页的指令。 具体设计中需注意以下事项 1。检查总线时序 控制信号是否提供了足够的读、写时间,要特别注意系统的时钟速率,因为控制信号的时序总是取决于时钟速率。如果总线控制信号速度过高,大多数微处理器能够展宽时钟,降低数据存储速率。 2。确认总线控制信号在上电或掉电时的状态 如果Vcc高于门限电压时CE=WE=0,当前地址的数据在没有正常写操作的情况下将被破坏。如果系统仅对本地可寻址空间寻址,要确保总线控制信号在复位状态处于禁止状态、保证数据不被破坏。当采用扩展寻址时,需保证I/O信号控制CE和WE在上电或掉电状态下均处于高电平。利用CPU监控电路能够保证微处理器在NVSRAM处于电池备份模式时不会访问NVSRAM。这时模块内的片选信号为高电平,与外部CE信号无关,模块内的SRAM将拒绝任何外部访问。 微处理器利用NVSRAM存储程序 利用NVSRAM存储程序时有两点值得特别考虑:1。NVSRAM必须具有足够快的存取速率、不需要降低时钟速度。2。Vcc低于电压监视门限时,不能访问NV SRAM。微处理器必须在每个机器周期取指令(通常每个机器周期占用一个以上的时钟周期),如果程序存储器速度较慢、需降低时钟速率以符合存储器存取速率的要求。显然,这种情况制约了系统性能。目前,5V高速NVSRAM的存取时间可以达到70ns,3。3V的NVSRAM可以达到100ns,能够符合大多数应用的要求。 利用复位门限接近Vcc的CPU监控电路能够避免微处理器在NVSRAM就绪之前对其进行读、写操作,此外,Vcc噪声有可能导致电压瞬间跌落至Vcc门限以下,造成器件在瞬间干扰时无法读取。鉴于这一点,建议在靠近模块的Vcc引脚安装去耦电容。由于市场上可以很容易找到5%电压容差的CPU监控芯片,因此,采用电压容差为10%的NVSRAM可简化设计,现有的3。3V和5V的器件均可满足这种要求。 如上所述,NVSRAM不适合作便携数据的载体,当器件脱离具有实际意义的电路时容易丢失数据。最好是在线进行器件编程,为解决嵌入式系统的在线编程问题,可以简单构建一个导入装载器,流程如图3所示。 导入器在切换存储器(从微控制器的内部EPROM切换到外部NVSRAM)时工作,存储器内部电路通过RS232端口接收数据,将数据复制到适当地址的NVSRAM内。实现该流程的简单数据格式是Intel的十六进制文件格式,因为这种对数据和数据地址的编码格式是许多汇编语言采用的标准文件格式。EA引脚置“1”,选择内部存储器,此时PC机可以通过一个RS232串口给微控制器发送数据。微控制器将代码写入NVSRAM后即可关闭电源、清EA引脚,当再次上电时微处理器便开始执行存放在NVSRAM内的代码。一旦完成了最初的硬件和软件开发,就可以方便地进行快速编程,大大缩短产品开发周期。这种方案的缺陷是对于不同产品的开发必须保持固定的晶振频率,以保证串行端口的波特率能够由PC机软件调节。

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- SHARC引领第四代通用DSP高端应用潮流(09-27)

- 在应用可编程测控网络设计(03-15)

- 基于dsPIC33F系列单片机的应用程序升级方法(04-03)

- 采用混合时钟模式提高Linux时钟精度的方法(05-10)

- MSP430低功耗原理及其在海温测量中的应用(06-06)