基于DSP开发系统设计与实现

时间:04-25

来源:互联网

点击:

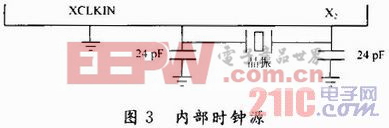

3 时钟电路设计

TI的DSP时钟电路分为三类:晶体电路、晶振电路和可编程时钟电路。其中时钟电路如图3所示。

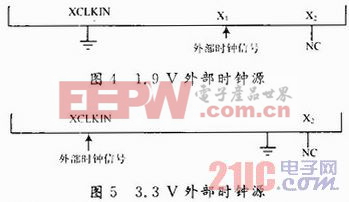

其特点是:结构简单,但频率范围较小,一般为20 kHz~60 MHz,驱动能力较弱。晶振电路利用外部独立的时钟源给系统提供时钟。其特点是:频率范围较大,一般为1 Hz~400MHz,驱动能力强,可为具有相同时钟的多DSP系统使用。可编程时钟电路可以为外设提供不同的时钟,适用于不同时钟源的系统使用,频带宽度可达 200 MHz。F28335的外部时钟可以有两种输入方法,如图4~图5所示。

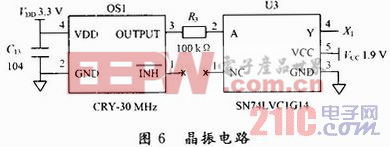

该设计使用1.9 V的外部时钟源晶振电路,如图6所示。其中,100Ω电阻用来衰减外部杂波的干扰,提高时钟波形的质量,SN74LVC1G14是单路施密特反向触发器。

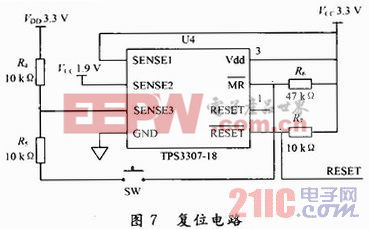

4 复位电路设计

复位电路是在系统上电或程序跑飞时对系统自动或手动的初始化。该设计采用TI公司推出的三端监控芯片TPS3307系列来实现系统初始化和电源监控功能。TMS320F28335采用1.8 V或1.9 V内核电压,3.3 V I/O电压。利用TPS3307-18来实现对系统的自动和手动复位。SEN SE1,SENSE2和SENSE3管脚分别对3.3V I/O电压、1.8 V内核电压和3.3 V模拟电压监控。手动复位引脚接至复位键,当按下时 变为低有效,实现手动复位的功能。具体电路如图7所示。在上电期间,当电源电压高于1.1 V时,

变为低有效,实现手动复位的功能。具体电路如图7所示。在上电期间,当电源电压高于1.1 V时, 开始有效,然后开始监控SESEN输入管脚的电压。当SENSE1,SENSE2和SENSE3分别低于门限电压2.93 V,1.68 V和2.5 V时,TPS3307-18的

开始有效,然后开始监控SESEN输入管脚的电压。当SENSE1,SENSE2和SENSE3分别低于门限电压2.93 V,1.68 V和2.5 V时,TPS3307-18的 向F28335发出低电平复位信号,实现自动复位的功能。

向F28335发出低电平复位信号,实现自动复位的功能。

基于DSP开发系统的PCB设计对最终系统的性能有着重要的影响。特别是对于DSP,管脚多且管脚间的间距小,导致布线时线间距受到限制,容易受到干扰。为了有效抑制干扰,在布局时输入时钟应尽可能靠近DSP,使其输入线路尽可能短,并使晶振外壳接地;为了减小芯片上的电源电压瞬时过冲,在电源的输入端使用去耦电容;电源是系统的主要干扰源,使用旁路电容及去耦电容来尽量减小电源对系统的影响。在设计中,可以利用0.1μF的电容来避免内在的振动和高频噪声,利用10~100μF的旁路电容减小电压输出的脉动。基于以上考虑,DSP开发系统才能够稳定可靠地运行。

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)