基于RocketIO接口的高速互连应用研究与实现

摘要:在此立足于嵌入式应用的背景,在理解RapidIO协议和Fibre Channel协议的基础上,通过对嵌入在FPGA内的RocketIO高速串行收发器工作原理的研究,结合某信号处理接口模块的实际应用,在系统内实现RapidIO接口功能,在系统间实现Fibre Channle接口功能,总结出基于RocketIO接口的高速信号完整性设计的应用特点,并进行简单的链路传输特性的测试,为高速互连系统的设计与研究提供了可靠的技术支撑。

关键词:RocketIO;RapidI();Fibre Channel;嵌入式应用

0 引言

近年来,多种新兴的高性能互连技术相继出现,如RapidIO,PCI Express,Fibre Channel和InfiniBand等,它们大都采用基于报文交换的点到点互连结构替代传统并行总线结构,提供了高带宽、低延迟、可扩展的I/O互连,很大程度上克服了传统并行总线结构的种种弊端。其中RapidIO属于系统内部互连技术,主要针对高性能嵌入式系统内部互连,它可以作为处理器总线、本地I/O总线,还可以跨越背板连接处理器、存储器和外部设备。RapidIO技术被定义为一种高性能,低引脚数,基于报文交换的互连体系结构,能广泛满足嵌入式系统应用的需求,支持芯片到芯片和板到板之间的互连技术。光纤通道(Fiber Channel,FC)是一种高速串行传输协议,具有高带宽、高实时性、高可靠性、扩展性好、传输速率高、抗干扰性强、拓扑结构和服务类型灵活、支持多种上层协议和底层传输介质等特性,且可以在一路传输线上实现高达2.5 Gb/s的速率,具有相对于万兆以太网,PCIe更高的传输速率。

在嵌入式应用方面,主流的FPGA中都已对差分信号提供了硬件支持,并且在片上集成了固化的Rocket IO模块,以提供高超高速的串行通信支持。RocketIO位于数据传输协议的物理层,用以实现最基本的数据通信环境。

本文从Xilinx的Virtex5系列FPGA的RocketIO高速串行收发器的工作原理入手,分别阐述了在一片FPGA上利用RapidIO协议和Fibre Chan nle协议实现高速信号传输的方法,并分析了RocketIO接口在硬件设计上需要注意的问题。

1 RocketIO介绍

RocketIO为FPGA中内嵌的硬核资源,是一种高速串行收发器,采用两对差分线来进行数据的发送和接收,可以实现两个单工或一对全双工的数据传输,通信码率可以达到600 Mb/s~3.125 Gb/s。RocketIO收发器发送和接收串行差分信号,工作于2.5 V的直流电压下,采用CML(Current Mode Logic)模式,内部带有50 Ω或75 Ω的匹配电阻,采用串行数据收发,可以在高频条件下很好地避免数据间的串扰。

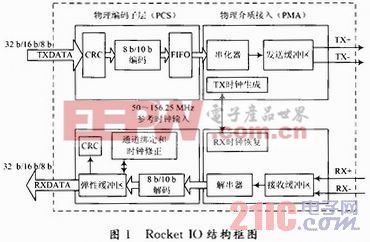

RocketIO收发器结构如图1所示,主要包括PMA和PCS两个子层,PMA子层中集成了SERDES,发送和接收缓冲,时钟发生器及时钟恢复电路。SERDES是一个串并转换器,负责FPGA中本地的32位并行数据(也可以是16位或8位)与Rocket IO接口的串行数据之间的转换。时钟发生器及时钟恢复电路用于将时钟与数据绑定发送及将时钟从接收到的数据流中恢复出来,从而避免了在高速传输条件下时钟与数据分开传输所带来的时钟抖动等问题。PCS子层负责8 b/10 b编码解码和CRC校验,并集成了负责通道绑定和时钟修正的弹性缓冲。8 b/10 b编码可以避免数据流中出现连0连1的情况,便于时钟的恢复。通道绑定通过在发送数据流中加入字符来将几个RocketIO通道绑定成一个一致的并行通道,从而来提高数据的吞吐率。弹性缓冲可以解决恢复的时钟与本地时钟不一致的问题,并进行数据率的匹配,从而使得通道绑定成为可能。

2 RocketIO在高速信号互连中的应用

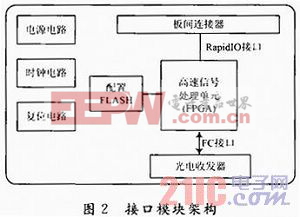

以某信号处理模块FC接口板卡为例,该模块是一种高性能、具有高速串行接口、采用统一互连网络的通用信号处理接口模块,信号传输速率达到几千兆位每秒,这时就需要具有足够高传输速率的信号传输机制对信号进行转发。实现与主机板卡通信时,采用RapidIO传输协议;实现系统网络间通信时,则可使用FibreChannle光纤通信协议。而RocketIO对多种高速传输协议的支持,可以使得RapidIO协议、Fibre Chan nle协议在同一片FPGA内实现,提高了系统的集成度,并使得信号的处理机制更加灵活。在本文的设计中,以Xilinx的Virtex5系列FPGA为平台,采用了RapidIO传输协议来实现与主机板卡的通信,采用Fibre channle协议来实现系统网络间通信。本文涉及的接口模块架构如图2所示。

2.1 应用RapidIO协议买现板间互连

RapidIO是一种基于高性能包交换的开放式互连技术,主要功能是完成系统内部芯片到芯片和板到板之间的高速传输数据,能够提供高带宽、低时延、软件独立和高容错性的数据传输解决方案。同时支持点对点或点对多点的通信、DMA操作、消息传递模式交换数据以及多种拓扑结构等功能。

RapidIO采用3层分级体系结构,分别为物理层、传输层、逻辑层。物理层规范在整个分级结构的底部,包括器件级接口的细节,如包传输机制、流量控制、电气特性和低级错误管理。传输层规范在中间层,定义RapidIO地址空间和在端点器件间传输包所需的路由信息。逻辑层规范定义全部协议和包的格式,它们为端点器件发起和完成事物提供必要的信息。

RapidIO串行物理层,通常称为串行RapidIO,是针对板上或通过背板的器件间的电气连接。串行物理层定义器件间的全双工串行链路,在每个方向上使用单向差分信号。RapidIO串行物理层实现链路训练、链路初始化,支持RapidIO器件间的包传送,包括包和控制符号的传送、流量控制、错误管理和其他器件到器件的功能。RapidIO物理层核与RocketIO收发器连接逻辑结构框图如图3所示。

研究 实现 应用 高速 RocketIO 接口 基于 相关文章:

- 基于DSP的音频会议信号合成算法研究(05-10)

- 基于定点DSP的MP3间频编码算法研究(07-04)

- DSP的并联电力有源滤波器的仿真研究(02-15)

- PCI总线数据采集系统的硬件研究(09-12)

- PIC单片机在温度测量领域的应用及仿真研究(11-23)

- 嵌入式软PLC 的设计与研究(06-27)