基于RocketIO接口的高速互连应用研究与实现

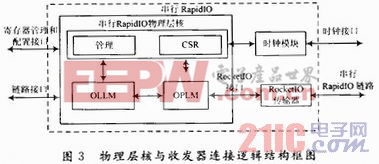

由于RapidIO逻辑层包被定义为一连串的比特,并且与物理层实现无关,所以RapidIO协议在串行与并行接口,铜线与光纤介质下都能正确工作。

其RapidIO串行物理层有如下特征:

(1)采用8 b/10 b编码方案将发送时钟嵌入到数据中。

(2)在每个方向上支持一个串行差分对或支持4个并列的串行差分对。

(3)使用专用的8 b/10 b码(称为K码)来管理链路,管理流量控制、包定界和错误报告。

(4)支持每通道1.25 Gb/s,2.5 Gb/s和3.125 Gb/s波特率(数据速率分别为1.0 Gb/s,2.0 Gb/s和2.5 Gb/s)的传送速率。

2.2 应用Fibre Channel协议实现系统间互连

光纤通道技术是综合计算机通道和数据网络概念提出的一个不同于传统的通道和网络结构的互连方案,采用通道技术控制信号传输,使用仲裁或交换方式处理共享冲突,并采用了基于信用的流量控制策略。

Fibre Channel模型分为5层,分别为:FC-0,FC-1,FC-2,FC-3和FC-4。FC-0层定义了连接的物理端口特性,包括介质和连接器、驱动器、接收机、发射机等的物理特性、电器特性和光特性、传输速率以及其他的一些连接端口特性。在本设计中,FC-0层处理由光电收发器实现光信号与电信号转换;FC-1层是信号编码和解码层,FC-1层处理由FPGA的RocketIO完成串并/并串转换、8 b/10 b编解码、有序集及位同步等;FC-1层使用8 b/10 b编码方式,这意味着每传输10 b数据,实际得到8 b的有效数据,其他两位是冗余位。信号可以被编码成2种字符集:K字符集(特殊的控制信号和命令)和D字符集(普通数据)。FC-2层是帧协议层,是FC用来识别、解释和处理FC网络信息流的核心层。FC-2层规定信息单元的组成格式、原语序列协议、端口类型、服务类型、数据的分段与重组、流量控制、差错恢复策略、节点初始化、节点的注册和节点的注销等功能。FC-0,FC-1和FC-2层这3层共同组成了FC物理层。FC-3层是FC的公共服务层,定义了如带宽频率分片、搜索组和多播等通用服务。FC-4:该层是FC协议模型的最高层,在本系统的设计中,使用了匿名签署消息传输协议(FC-AE-ASM)来满足系统中数据的传输需要。

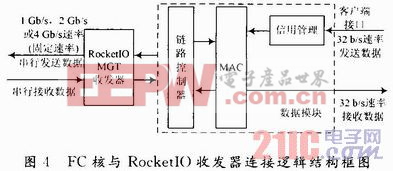

在FC核的嵌入式应用中。使用一个或2个RocketIO收发器来提供1 Gb/s,2 Gb/s或4 Gb/s的接口速率,利用FPGA中的8 b/10 b编解码器、CRC产生和校验单元以及接收弹性缓冲进行设计。FC核内部提供了32 b宽的Client接口,FC帧数据采用32 b/s访问。FC核的时钟在配置时已固定,分别可采用53.125 MHz和106.25 MHz。

FC核与RocketIO收发器连接逻辑结构框图如图4所示。

3 RocketIO接口的信号完整性设计

在实际应用中,参考时钟、电源供电以及高速传输线路的设计与布局是影响数据传输效果的最重要因素。为了保证Rocket IO能可靠工作,在RocketIO接口设计过程中需要注意以下的问题:

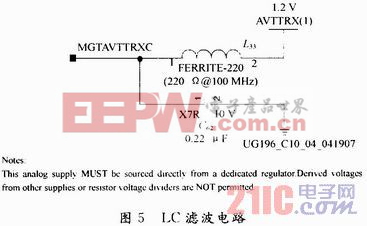

(1)电源供电。该系列FPGA器件中每个RocketIO高速串行收发器包括5类电源引脚,分别为MGTAVCCPLL,MGTAVCC,MGTAVTTRX,MGTAVTT TX,MGTAVTTRXC,这些引脚对噪声的影响都非常敏感,为了保证高速电路能够可靠工作,RocketIO需要和周围的噪声源进行隔离。因此需要对RocketIO收发器进行专门的供电,且每个供电引脚必须有独立的LC滤波网络,其连接关系如图5所示。

(2)高速信号。RocketIO高速串行收发器采用高速差分信号线,由于所传输的差分信号频率很高,高速差分对走线应当有最高的优先级,两根差分信号线必须在长度上尽量匹配,长度失配会产生共模噪声和辐射,严重的失配会产生时钟抖动和不可预知的时序问题,差分线必须尽量匹配,端接电阻50 Ω和75 Ω可选,50 Ω用于芯片和芯片之间互连,75 Ω用于芯片和电缆之间互连;高速差分线不要打孔,要布在电路板中同一层。

(3)参考时钟。RocketIO不能使用经过数字时钟管理模块(DCM)倍频的参考时钟,因为DCM倍频会引入过大的时钟抖动,在RocketIO的高速数据传输条件下会引起不必要的错误。RocketIO的时钟由差分时钟输入后,只经过一级BUFG,将时钟引入FPGA的全局时钟树,然后直接连入到RocketIO的参考时钟引脚上。

4 测试验证

在完成硬件设计后,可利用ChipScope Proh分析工具测试RocketIO的工作性能,通过内置在收发器内的误码率测试器,设置RocketIO为串行闭环方式,并运行软件进行测试即可得到实时的数据传输状态。如图6所示可观察到链路上的传输特性,并可得误码率可达到10-12,符合设计指标要求。

本文从Virtex5系列FPGA的RocketIO高速串行收发器入手,根据接口设计需要阐述了应用RapidIO协议和FC协议实现高速传输的设计思想及工作原理。并分析了高速传输在硬件设计过程需要注意的一些问题,为高速接口设计的研究奠定了基础,具有一定的科研价值和实践意义。

研究 实现 应用 高速 RocketIO 接口 基于 相关文章:

- 基于DSP的音频会议信号合成算法研究(05-10)

- 基于定点DSP的MP3间频编码算法研究(07-04)

- DSP的并联电力有源滤波器的仿真研究(02-15)

- PCI总线数据采集系统的硬件研究(09-12)

- PIC单片机在温度测量领域的应用及仿真研究(11-23)

- 嵌入式软PLC 的设计与研究(06-27)