基于ASIC FPGA的IPv6路由器PoS接口设计

FPGA选用Xilinx公司VIRTEX-II PRO,该电路是300万门级的FPGA,其高速I/O模块可提供多达16路Rocket I/O,内置Power PC核提供高性能的数字时钟管理,并且具有强大的开发软件支持。

4 实现方案

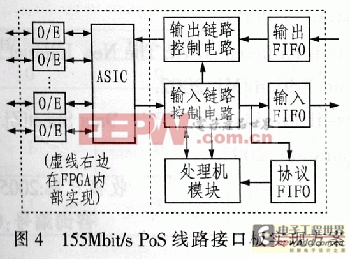

图4为155Mbit/s PoS接口的实现方案图。在输入方向上,从光纤传入的信号经光电转换后送入PM5380,完成定时处理、帧同步,从输入比特流中提取出SDH帧并进而恢复出PPP帧,并按接口缓存于内部8个FIFO中。输入链路处理模块轮询读取PM5380的FIFO,获得PPP帧并完成PPP相关处理,恢复出IP报文并且完成查IP地址表的工作,将协议报文交处理机,而普通的数据报文合路输入FIFO,进而通过FPGA的Rocket I/O(高速I/O)送转发处理。

在输出方向上,从转发过来的数据报文 经Rocket I/O送FPGA内部,在输出链路处理模块中完成与协议报文的合路并且封装成PPP帧,然后根据内部报文格式中的出接口号来判断送往ASIC的哪个接口; ASIC完成SDH帧的映射,最后经电光转换通过光纤送到外部SDH网络。

5 FPGA设计

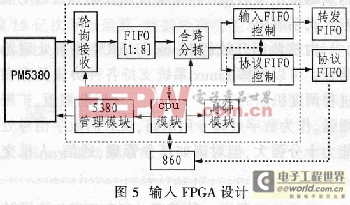

图5中的虚线框内为输入FPGA设计原理。输入FPGA的轮询接收模块从PM5380的FIFO中轮询读取8个外部接口的数据,并将完整的PPP包缓存;分拣模块查本地IP表,将协议报文缓存于协议FIFO并经处理机送交主控处理,需转发的数据报文送转发FIFO。图中的MPM5380管理模块负责产生处理机管理PM5380时所需要的时序,CPU模块负责和860的交互,时钟模块产生系统时钟,它们是公共模块。

图6示出输出FPGA设计原理。从转发过来的数据经Rocket I/O后缓存于输出FIFO,合路模块将数据报文和从处理机下发的协议报文合路送发送模块按照PM5380要求的时序写到相应接口的FIFO中发送,但这里必须严格满足PM5380的写时序要求。

6 结束语

本文根据IPv6路由器155Mbit/s PoS接口的需求,提出并实现了一种基于ASIC+FPGA的设计方案。目前该方案已经在国家数字交换系统工程技术研究中心开发的IPv6路由器中得到实现,测试后的系统性能稳定,达到了预期的设计目标。

- 基于IPv6的嵌入式互联网视频应用开发(02-07)

- 基于Linux的IPv6复合防火墙的设计(05-28)

- 基于S3C2440的嵌入式IPv6防火墙设计(09-02)

- 大热的嵌入式视频系统的设计与实现方案汇总,提供(09-12)

- 电动车充电智能化挑战 G3-PLC技术解决(01-16)

- 基于S3C2440的嵌入式IPv6防火墙设计(二)(09-14)