SoC系统中AHB/VCI Wrapper的设计及验证

摘要:文章描述SoC平台的片内总线到VCI标准接口的转换部件的设计实现。它可以把带有VCI标准接口的IP模块和AMBA AHB系统总线连接起来。研究内容主要包括两部分:第一,在VCI标准Rev2.0版本的基础上,参照BVCI协议要求完成一个AMBA AHB系统总线与VCI标准接口的转换部件-AHB/VCI Wrapper;第二,利用总线功能模型(BFM)思想,为AMBA总线和BVCI接口建立相应的BFM模型,在此基础上,完成对AMBA总线控制部件和AHB/VCI Wrapper的功能验证。该平台具有很好的可重用性。

关键词:AMBA总线;VCI接口;总线功能模型

0 引言

Basic VCI协议:AHB/VCI Wrapper的设计中采用的是VCI接口标准中的Basic VCI(BVCI)。

SoC平台通过提供预先集成并验证好的特定应用IP核,在很大程度上减弱了IP系统集成和系统级验证的负担。SoC设计平台中各功能IP模块是通过AMBA总线来连接的。AMBA(Advanced Microcontroller Bus Architecture)Rev2.0片内总线由ARM公司开发,是业内广泛流行的一种工业标准片内总线。

1 AHB/VCI Wrapper设计思想

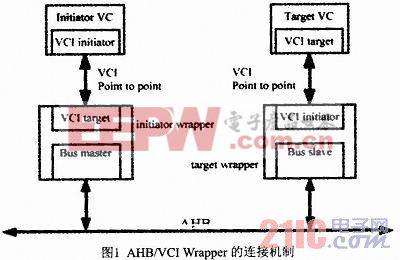

它包含两部分:AHB-initiator-Wrapper和AHB-target-Wrapper,如图1所示。从而实现AHB主设备与VCI从动方以及AHB从设备与VCI主动方之间的协议相互转换。

AHB-initiator-Wrapper负责把VCI请求转换成AHB周期请求,此时,它在AHB总线方相当于一个AHB主设备,在VCI方相当于一个VCI从动方。由于AHB-initiator-Wrapper具有AHB主设备特性,因此它在实际应用中可被例化为多个VCI主设备接口。

AHB-target-Wrapper负责把AHB传送转换成VCI传送,此时,它在AHB总线方相当于一个AHB从设备,在VCI方相当于一个VCI主动方。同样,由于AHB-target-Wrapper具有AHB从设备特性,因此它在实际应用中可被例化为多个VCI从设备接口。

1.1 AHB initiator Wrapper的设计

AHB-initiator-Wrapper负责接受VC主动方发出的请求,并控制AHB总线(作为总线主设备)完成传送。尤其是,AHB-initiator-Wrapper要负责向AHB总线仲裁器请求总线所有权,得到总线以后,启动AHB上的传送并处理相应的AHB传送反应,最后完成数据传送。

1.2 AHB initiator Wrapper的总体构架

本设计中的AHB-initiator-Wrapper采用同步化电路机制解决了VCI主动方设备与AHB总线之间的速率匹配问题,图2给出了该设计的总体构架。它主要包含五部分:BVCI请求握手控制单元、BVCI响应握手控制单元、请求内容FIFO、响应内容FIFO和AHB主设备控制引擎。

BVCI请求握手控制单元按照BVCI请求握手协议接受来自BVCI主动方的请求内容信息,并把它们插入请求内容FIFO(速率不匹配情况)或直接传送到AHB控制一侧(速率匹配情况)。

BVCI响应握手控制单元从响应内容FIFO中取出BVCI响应内容信息,并按照BVCI响应握手协议把它们驱动到BVCI主动方。

请求内容FIFO是一个异步FIFO(写端口与读端口分别工作在不同的时钟域),它只有当VCI主动方设备和AHB总线之间速率不匹配时才工作。

响应内容FIFO为一个异步/同步模式可配置的FIFO,当VCI主动方设备和AHB总线之间速率不匹配时,它工作在异步模式(写端口与读端口分别工作在不同的时钟域)否则FIFO工作在同步模式(写端口与读端口工作在同一时钟域),只需完成BVCI响应内容信息的缓存功能即可。

AHB主设备控制引擎在BVCI和AHB之间进行控制信号的转换。还支持AHB主设备所具备的对总线异常传送(错误、重试传送)情况的处理能力。

1.3 AHB target Wrapper的设计

AHB-target-Wrapper作为一个AHB从设备,其主要作用是把AHB传送转换为符合VCI协议的传送。

1.4 AHB target Wrapper的总体构架

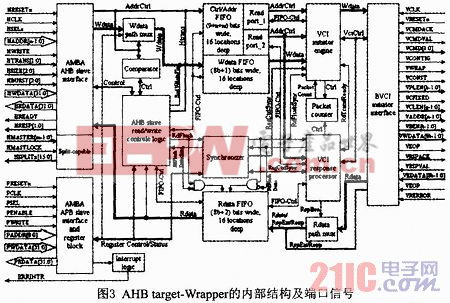

图3给出了AHB-target-Wrapper的总体构架,它由各种控制逻辑、数据通路、数据缓冲单元和寄存器组成,主要包含十三部分:寄存器块、AHB从设备读写控制逻辑、地址/控制信息FIFO、写数据FIFO、读数据FIFO、VCI主动方引擎、VCI响应处理机、比较器、包计数器、同步装置、写数据路径选择复用器、读数据路径选择复用器和中断逻辑。

(1)寄存器块完成对AHB-target-Wrapper的配置和控制以及对其当前工作状态的反应。

(2)AHB从设备读写控制逻辑,具备AHB总线从设备的控制功能。

(3)地址/控制信息FIFO主要用来存放AHB传送单元的地址/控制信息,以起到缓冲目的。

(4)写数据FIFO主要用来存放进行写操作时的数据,以起到写数据缓冲目的。

(5)读数据FIFO主要用来存放进行读预取操作时的数据,以起到读数据预取目的。它也是一个双端口的同步/异步可配置FIFO(一个写端口,一个读端口),当AHB总线和VCI从动方设备之间速率不匹配时工作在异步模式下,匹配时工作在同步模式下,同步/异步模式的切换可通过配置寄存器来实现。

(6)VCI主动方引擎把符合AHB传送协议的地址/控制信息转换为符合BVCI标准的请求内容信息,并按照BVCI请求握手协议把请求内容信息驱动到VC从动方设备。

(7)VCI响应处理机按照BVCI响应握手协议接收由VCI从动方设备返回的响应内容信息,并进行相应的处理。

(8)比较器用于读预取操作情况,比较正在进行的读预取操作和AHB上新发来的读操作是否为同一个读交易。

(9)包计数器用来统计当前VCI主动方引擎发出的多个BVCI请求包中没有被响应的请求包个数,其主要目的是为VCI主动方引擎提供有关当前请求包是否正在被响应的信息。

(10)同步装置在两个时钟域的交叉处,即从HCLK到VCLK域和从VCLK到HCLK域的两个数据流方向上,分别对内部控制信号进行同步。

(11)写数据路径选择复用器根据AHB的传送单元大小、字节地址和地址大小端模式来选择AHB写数据总线上相应的字节通道并把它复制到没选通的字节通道上。

(12)读数据路径选择复用器根据BVCI响应字节使能(按照一定的算法,由AHB读交易的传送单元大小、第一个传送字节地址以及BVCI的地址模式自动转换生成)来选择BVCI读数据总线上相应的字节通道并把它复制到没选通的字节通道上。

(13)中断逻辑当内部电路在执行写操作过程中发生传送错误时,产生错误中断源,同时根据中断屏蔽寄存器来决定相应的中断源是否开放,根据中断清除寄存器来清除相应的中断源。

2 AHB/VCI、Wrapper的硬件实现

本文分别给出了AHB-initiator-Wrapper和AHB-target-Wrapper的总体构架,并对两者内部的各个功能模块及控制部件的结构设计进行了详细叙述,同时对两者的可配置性也进行了充分考虑。在本章最后,对AHB/VCI Wrapper进行了RTL级Verilog硬件建模并进行了初步的门级综合及电路规模预估。

3 验证平台的搭建

本节的BFM模型主要任务就是利用这些模型来搭建验证平台。

把AHB主设备BFM模型、VCI从动方BFM模型、系统时钟及复位产生模型、待测设计AHB-target-Wrapper模块和AMBA总线控制器进行适当组合,集成在一起便可构成验证平台,如图4所示。这个过程需要由TestBencher Pro工具来完成,因为该工具可以很好地控制BFM模型中每个命令函数的调度和执行顺序,其自动化程度是比较高的。剩下需要由设计者做的事情是,根据待测设计AHB-target-Wrapper的测试要求,编写平台脚本来合理安排BFM模型中每个命令函数的调度和执行顺序,然后以文件形式输入到验证平台中即可开始进行验证。该验证平台通过Test Bencher Pro工具生成之后,也可以移植到别的模拟器环境中运行。

设计 验证 Wrapper VCI 系统 AHB SoC 相关文章:

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)