基于ARM的高精度数据采集系统设计

流最近,以避免对模拟电路的干扰,提高系统的采集精度。模拟地和数字地可以通过磁珠连接,由于磁珠的高频阻抗大,而直流电阻为零,能够滤除高频电流减少地线上的高频噪声。

(4)防止空间电磁辐射对系统的干扰:由金属材料做成屏蔽罩,将器件屏蔽起来,并将屏蔽罩妥善接地。

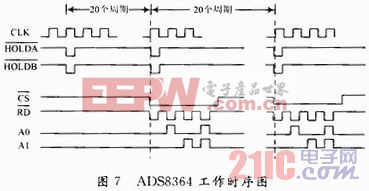

4 数据采集的时序控制

对该A/D芯片CLK的要求为小于5 MHz即可,本方案结合ARM的处理能力,选用1 MHz的时钟,A/D芯片每20个时钟周期完成一次转换,采集率为50kHz。时钟信号CLK可以一直输出。CLK为上升沿触发。芯片上电后,首先进行复位操作,将 置为低电平并保持宽度50ns以上,之后一直将RST置为高电平。

置为低电平并保持宽度50ns以上,之后一直将RST置为高电平。 ,

, 平时一直为高电平,当需要采集的时候,将

平时一直为高电平,当需要采集的时候,将 同时置为低电平,并将

同时置为低电平,并将 保持时间为50 ns到半个时钟周期的宽度,之后

保持时间为50 ns到半个时钟周期的宽度,之后 信号恢复到高电平。此时完成输入端信号的锁存。经过20个时钟周期后,4个通道都已完成模/数转换,并把转换结果放在输出端对应的寄存器内。下一步要做的就是把寄存器内的数依次取出,读进单片机里。将

信号恢复到高电平。此时完成输入端信号的锁存。经过20个时钟周期后,4个通道都已完成模/数转换,并把转换结果放在输出端对应的寄存器内。下一步要做的就是把寄存器内的数依次取出,读进单片机里。将 置为低电平,将

置为低电平,将 置为低电平,并将AO,A1,A2同时置为0,0,0,之后经过40 ns后,通道1的数据便放到了16位数据总线上。单片机可以进行读取。的宽度可以和时钟一样,当变为高电平时,单片机读取16位数据总线上1通道的转换结果。随后

置为低电平,并将AO,A1,A2同时置为0,0,0,之后经过40 ns后,通道1的数据便放到了16位数据总线上。单片机可以进行读取。的宽度可以和时钟一样,当变为高电平时,单片机读取16位数据总线上1通道的转换结果。随后 变为低电平,并将A0,A1,A2同时置为0、0、1,之后经过40 ns后,通道2的数据便放到了16位数据总线上,随后在为高电平时将数据总线上的2通道的数据读走。然后依次时序继续读取通道3和通道4的数据。4个通道的时序都读取结束后,将

变为低电平,并将A0,A1,A2同时置为0、0、1,之后经过40 ns后,通道2的数据便放到了16位数据总线上,随后在为高电平时将数据总线上的2通道的数据读走。然后依次时序继续读取通道3和通道4的数据。4个通道的时序都读取结束后,将 置为高电平,将

置为高电平,将 置为高电平。工作时序图如图7所示。

置为高电平。工作时序图如图7所示。

5 结语

本系统设计以低功耗、小尺寸、低成本和高精度为目标。介绍系统时钟电路设计、ADC单元设计、电源设计、抗干扰设计及数据采集的控制时序设计。设计的难点在于高精度并行A/D采集模块与ARM芯片的通信及时序控制问题。调试结果表明该方案工作性能强,体积小,成本低,非常适用于小型化、低成本的数据采集领域。

- Linux嵌入式系统开发平台选型探讨(11-09)

- VxWorks实时操作系统下MPC8260ATM驱动的实现(11-11)

- VXWORKS内核分析(11-11)

- Linux内核解读入门(11-09)

- linux文件系统基础(02-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)