基于ARM的高精度数据采集系统设计

摘要:针对传统数据采集系统结构复杂,体积大,成本高的问题,设计了一种基于ARM的新型、低成本、高精度数据采集系统,并提出了该系统的设计方案。详细论述了数据采集系统的硬件实现方案、抗干扰措施及控制时序,重点分析了高精度并行A/D的工作时序。实际应用结果表明,该数据采集系统精度高,体积小,成本低,工作性能强,具有较高的实用价值和借鉴意义。

关键词:ARM;高精度;数据采集系统;抗干扰

目前,高精度数据采集系统的结构普遍采用DSP+FPGA的构架,系统结构复杂,体积大,成本高,不适用于某些领域的小型化、低成本的特殊要求。综上,设计了一种结构简单,体积小,成本低,采集精度高的数据采集系统,具有非常重要的现实意义及应用前景,能够为国内数据采集系统开发提供一定的经验和参考。

1 数据采集处理系统的工作原理和结构

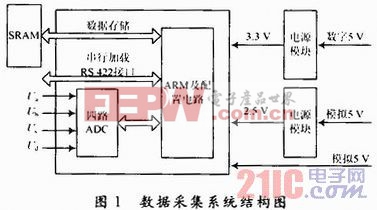

嵌入式微处理器ARM具有外围配置电路简单、体积小、成本低、性能高、可靠性高和外围硬件资源丰富等优点,能够保证数据采集的实时性,而且还有较强的数据处理功能,在诸多领域的应用日趋广泛。本方案中模/数转换芯片选用16位ADS8364,系统主芯片选用意法半导体公司推出的基于ARM Cortex-M3系列32位芯片STM32F103ZET6,主频为72 MHz,工作电压为2.0~3.6V,I/O电压为3.3V。112个通用I/O端口,3个SPI通信接口,2个I2C通信接口,5个USART通信接口,1个USB接口,1个CAN通信接口,4个通用16位定时器和2个PWM定时器,内置512 KB FLASH ROM和64 KB RAM。

数据采集系统的工作原理:当ARM芯片发出采集指令的时,将模拟信号采集到主芯片中,并进行后续解算,同时将采集到的信息存贮到外置超大SRAM中,以备后期分析处理。系统结构图如图1所示。

2 硬件电路设计

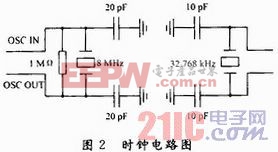

2.1 时钟电路设计

主芯片有2个外部时钟源,电路如图2所示,32.758 kHz的晶体是一个低速外部晶体,它能为实时时钟部件(RTC)提供一个低速但高度精确的时钟源。8 MHz外部晶振作为系统的时钟源,经过倍频后变成72 MHz为ARM提供时钟。

2.2 复位电路

系统复位有多种方式:NRST引脚上出现低电平(外部复位);窗口看门狗计数终止条件(WWDG复位);独立看门狗计数中止条件(IWDG复位);软件重围(SW复位);低电源管理复位。本方案中采用第一种复位方式,只需在外部加复位开关,方式简单,便于操作。

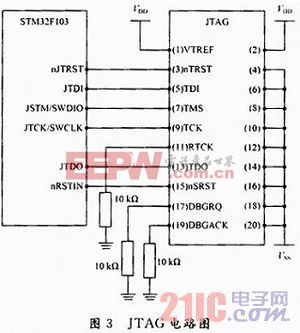

2.3 JETG接口

仿真接口为JTAG形式,实现对STM32F103ZET6的仿真与调试。电路图如图3所示。

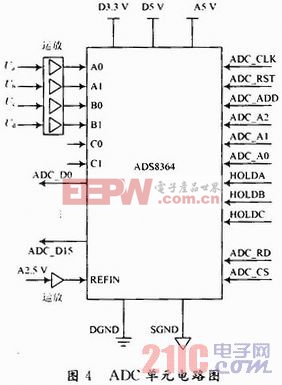

2.4 ADC单元

ADC单元主要功能是完成对A/D芯片时序控制及数据读取,并将数据缓存在寄存器中,供处理功能单元进行运算处理。因为输入电压范围是0~+5 V,且要求分辨率不大于2 mV,所以要求ADC的有效位数至少为12位,考虑到ADC的转换误差,将ADC的输出数据位数定为16位。由于ADC单元用于采集4路接近直流的信号,所以对ADC的采样率要求较低,这里将采样率定为50kHz。

ADC单元主芯片选用TI公司的ADS8364,该芯片有16位数据线,6路输入通道,最高转换速率250 kHz,输入信号0~5 V,外接电压基准源2.5V,具有3.3 V兼容的数字接口,其引脚可以直接和ARM芯片STM32F103ZET6的I/O接口相接。ADC芯片挂载在STM32F103ZET6的I/O接口上,通过I/O接口进行时序控制和数据读取。电路图如图4所示。

2.5 RS 422串口通信单元

串口芯片采用MAX3160完成电气性能转换,连接在ARM芯片的USART通信接口上。该单元为RS 422通信接口,串行接口速率定为115.2 Kb/s,完成参数的串行加载功能。

2.6 电源电路

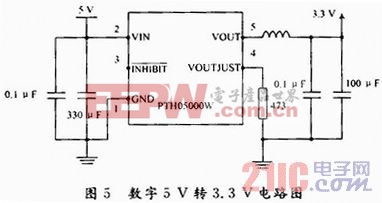

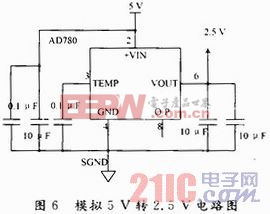

电源部分采用1片PTH05000W模块将输入的数字5 V电源转换为3.3 V,见图5。输入的模拟5 V电源用于给ADC电路供电。用一片AD780将模拟5 V转换为2.5 V,用于给ADC电路提供精密电压基准源,见图6。

3 抗干扰设计

A/D转换过程中,会遇到被采集信号小而干扰噪声强的情况,干扰有来自器件温度变化、接触电阻、引线电感、接地和电源等。因此,在整个数据采集系统设计中,要特别注意抗干扰的设计,根据具体的采集系统,本方案中主要考虑了以下几方面:

(1)合理设计印制板:根据硬件功能进行模块化布局,数字部分和模拟部分要分开,使用多层板,电源层和地层相互独立,电源线和地线要相对加粗;合理走线,避免信号线与高频线近距离平行走线。

(2)电源设计方面:在设计每个芯片的供电电路时,在每个芯片的电源附近并联去耦电容和旁路电容。

去耦电容为芯片提供局域化的直流,旁路电容可以消除高频辐射噪声和抑制高频干扰。

(3)接地方面:模拟地和数字地应严格分开,最后单点共地。共地点选择在ADC芯片管脚所需电流最大的位置,这样可以使大电流对地回

- Linux嵌入式系统开发平台选型探讨(11-09)

- VxWorks实时操作系统下MPC8260ATM驱动的实现(11-11)

- VXWORKS内核分析(11-11)

- Linux内核解读入门(11-09)

- linux文件系统基础(02-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)