基于FPGA的IPV6数字包的分离与封装的实现

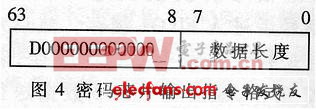

毕之后,在送出处理数据前,首先向外部系统发送一64bit长的连接指令,指明处理数据所用的加解密算法和数据长度。例如,在对数据进行2DES加密处理的情况下,接收指令格式(16位制)如图4所示,其中高56位为指令编码,低8位为将要输出的处理数据的长度。

因此,在接收处理数据时,首先判断是否有接收指令,如果有接收搦令,则其接收指令中的数据长度放寄存器中进行寄存,并设定计数器COUNTER2开始计数。当0

这时,包头已经缓存到FIFO3中了,处理后的数据已经按格式要求缓存到FIFO4中了,最后要做的就是控制FIFO3和FIFO4,把一个完整的IPV6数据包写入FIFO5中。具体做法是:设定计数器COUNTER3,当FIFO3和FIFO4都非空时,COUNTER3开始计数。当COUNTER3>0时,将FIFO5的写使能信号WR_EN5置为有效;当COUNTER3=0时,WR_EN5置为无效。当0l=6时,令RD_EN3无效,RD_EN4有效,将FIFO4的输出数据DOUT4(65~0)写入FIFO5的输入端DIN5(65~0),直到DOUT4(65~64)=“01”时,将COUNTER3清零,RD_EN4置为无效。这样,一个完整的IPV6数据包就重封装在FIFO5中了,当判断到FIFO5非空间,就可以令RD_EN5有效,向外输出处理后的完整的IPV6数据包了。

从上述讨论可以看出,本课题在FPGA中采用了五个FIFO,并设定了三个计数器控制这五个FIFO的输入输出来实现对IPV6数据包的拆分和重新封装。总的来看,整个FPGA设计思路巧妙,电路结构简单,达到了预期的处理速度。图5是整个测试系统在对1024字节的IPV6数据包进行拆包、送密码芯片加密。重装封装处理后测试仪控制软件界面上显示的收包数据统计。从该图可以看出,整个系统对IPV6数据包的处理速度达到了2.372Gbit/s,而这样的处理速度用软件是不可能达到的。

封装 实现 分离 数字 FPGA IPV6 基于 相关文章:

- 烧录器编程器夹具的重要性(06-02)

- FPGA最小系统之:硬件系统的调试方法(06-05)

- 从入门到开发,STM32F407单片机全中文教程(06-04)

- USB 3.0接口定义及封装介绍(12-12)

- 第53节:指针让一个函数可以封装多个参数(11-22)

- 单片机的标号信息及封装类型(11-17)