基于单片机及CPLD的多间隔脉冲产生电路

时间:06-06

来源:互联网

点击:

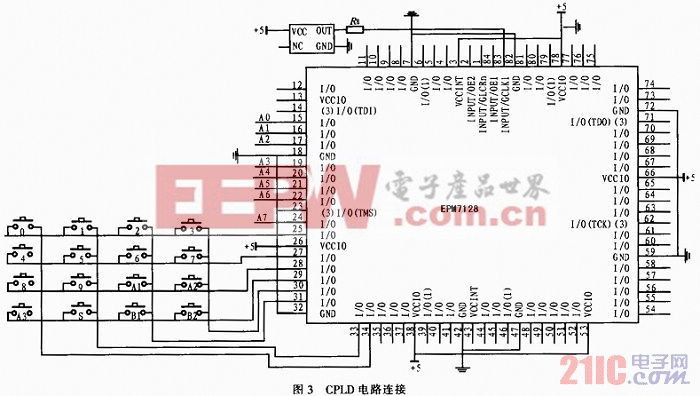

2.2 CPLD电路设计

晶振是为处理器提供频率基准的元器件,属于系统不可或缺的一部分。通常分为有源晶振和无源晶振两个大类,无源晶振要求芯片内部有震荡器,并且其信号电压根据起振电路而定,允许不同的电压,但无源晶振通常信号质量和精度较差,需要精确的匹配外围电路,如需更换晶振要同时更换外围电路。有源晶振不需要芯片的内部振荡器,可以提供高精度的频率基准,信号质量也较无源晶振要好。

EPM7128SLC84需要提供外部时钟信号,由于CPLD对时钟精度要求甚高,通过前面的分析可知有源晶振的通信质量和精度较无源晶振高,所以采用1.000 MHz的有源晶体振荡器,电路的输出端口与处理器EPM7128SLC84的GCKL1连接,其具体电路设计如图3所示。

3 系统软件设计

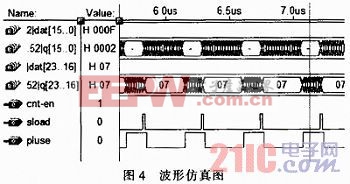

单片机采用AT89S52芯片,通过软件编程产生所要求的控制信号。主要的控制参数包括:信号周期、脉宽、分频电路的开始信号、地址发生器的复位信号。在MAX+PLUSⅡ开发环境中完成分频电路设计,可以省去大部分的中小规模集成电路和分离元件;使得电路具有集成度高、工作速度快、编程方便、价格低廉的显著优点。通过CPLD和数据预生成的信号实现方法,无需改变硬件电路,即可实现信号参数的任意调整;同时外围电路十分简单,为工程调试和应用带来了方便。其中波形仿真图如图4所示。

4 结论

所设计的脉冲信号发生器,充分利用了单片机及CPLD二者的优点,通过软件和硬件的结合,能够产生脉宽固定1μs,周期可调的单头、双头、三头脉冲,达到了设计要求,既可以作为普通脉冲信号源使用,也可以在一些特殊信号的条件下使用。 |