基于ARM和FPGA的时间同步仪控制单元设计

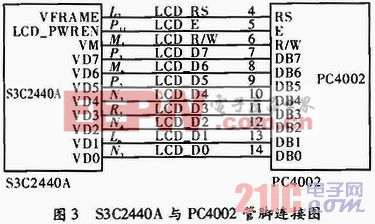

S3C2440A具有支持LCD的引脚,可以直接与PC4002进行连接,而且其BIOS中已经嵌套配置支持LCD,如图3所示。在物理链接上控制板与LCD通过背板进行信号通信。使用8 bit I/O读写进行数据交换。PC4002使用并行端口连接,占用从0X378h开始的8个I/O寄存器,其中0378h作为数据寄存器,0379h作为状态寄存器,037A作为控制寄存器。

2.4 以太网接口电路设计

网络传输模块使用Devicom公司研发的一款快速以太网控制芯片DM9000A,其内部集成了10/100 MB物理层接口,支持8/16位数据总线,内置16 kB的SRAM,用于收发缓冲。

S3C2440A内部没有集成专用的以太网控制器,所以需要外挂一个以太网控制器。系统采用DM9000A作为以太网的物理层接口。S3C2440A与DM9000A的连接如图所示。S3C2440A的数据总线LDATA15~LDATA0与DM9000A的SD15~SD0连接;地址线LADDR3与DM9000A的CMD连接;片选DM_CS与DM9000A的CS连接;DM_IOR/DM_IOW分别与DM9000A的IOR/IOW连接;EINT8与DM9000A的INT连接。以太网控制器DM9000A的工作地址为0X30 0,因为S3C2440A的地址线LADDR3与DM9000A的CMD连接,所以对其进行操作时分为以0X300作为地址端口和0X304作为数据端口。

2.5 RS232接口电路设计

S3C2440A集成了3个串口UART0、1、2,文中用到UART0,UART1,其中UART0作为标准串口通信,与宿主机相连用于系统调试、超级终端控制和文件收发;UART1与单片机ATMEGA128连接,其作用是传递导航电文和状态参数给GSG单板。图4为S3C2440A与RS-232信号连接图,其中上方的MAX3232SOP作为UART0使用,下方的MAX3232SOP作为UART1使用。

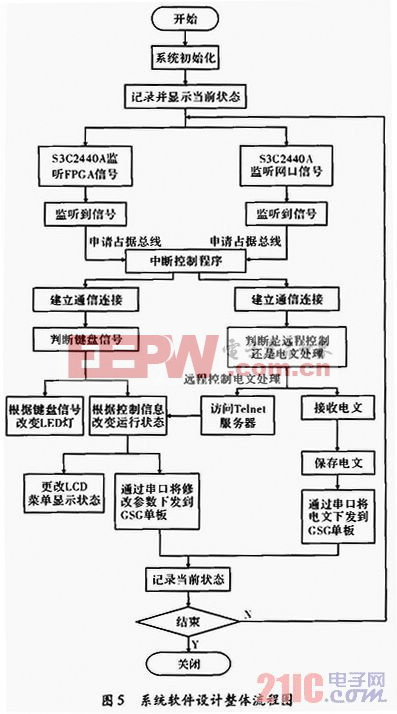

系统的软件部分是在Linux操作系统下实现的。结合控制系统的功能分为人机交互、参数设定、电文处理、远程控制4个模块,图5为软件设计流程图。

(1)人机交互模块。通过LCD设备提供系统的操作菜单显示,利用键盘操作完成用户的直接操作,同时利用机箱前面板上的LED指示灯向用户显示系统的工作状态。S3C2440A处理器接收从FPGA传送来的由键盘生成的相应控制指令,判断控制指令并且根据控制指令更改操作菜单、参数设定、状态信息。在液晶显示器上实时显示系统的状态信息和参数信息等,以保证正常的人机交互,如图6所示。

(2)参数设定模块。根据人机交互模块判断的控制指令设定系统的工作参数,通过RS-232收发器完成控制单元与GSG单板进行通信,将保存的导航电文发送到GSG单板的FPGA中,进行参数设定和改变发射状态。

(3)电文处理模块。通过以太网MAC控制器DM9000与外部主机进行网络通信,接收导航电文,在控制RS-232收发器与GSG单板进行通信,将收到的导航电文发送到GSG单板的FPGA中进行调制。如图7所示为得到GSG产生的在S码的波形图。

(4)远程控制模块。远程控制服务通过网络完成,用户可以使用计算机超级终端程序,连接时间同步仪对其进行控制。利用远程客户端,经过身份识别后获得对时间同步仪的控制权,从而进行参数设定、工作状态设定等操作。图8所示为远程控制界面。

采用S3C2440A为主控制单元,FPGA为辅助控制单元,实现了时间同步仪控制单元的设计要求:人机交互模块实现了键盘控制,LCD显示以及多级菜单功能。参数设定模块通过改变状态得到了相应的波形图结果。电文处理通过注入电文与GSG单板FPGA引出信号比对测试,验证了电文处理的正确性。远程控制模块通过Telnet软件测试得到了预期的控制结果。

控制 单元 设计 同步 时间 ARM FPGA 基于 相关文章:

- μC/OS-II下通用驱动框架的设计与实现(07-23)

- DSP和PBL3717A构成的步进电机的控制系统(04-01)

- 基于DSP的新型弹载控制计算机(04-05)

- 基于DSP的谐波控制器的研制(04-09)

- 数字信号控制器在变频家电中的应用(05-15)

- 基于DSP的磁流变阻尼器的控制方法(04-14)