FPGA平台的实时图像处理系统设计

摘要:本文提出了一种基于FPGA的实时图像处理系统设计方案。介绍了系统硬件结构设计和器件选型方案。并着重介绍了FPGA内部功能模块的设计,使整个处理系统既可支持大数据量的实时传输,又能满足图像数据实时处理的需要。

概述

在视频信号处理过程中为保证实时性,首先要求实时图像处理系统具有处理大数据量的能力。其次对系统的对外接口、功能、稳定性等也有严格的要求。实时图像处理算法中经常要用到对图像的求和、求差运算、二维梯度运算、图像分割、边缘探测等不同层次、不同种类的运算。有的运算结构比较简单,但是数据量大,计算速度要求高;有些运算对速度要求并不高,但计算方式和结构比较复杂,难以用纯硬件的方式实现。因此,实时图像处理系统是要求运算速度高、运算种类多的综合性信息处理系统。

图像处理系统中,底层的图像预处理的数据量很大,要求处理速度快,但运算结构相对比较简单,适用于FPGA通过硬件实现,这样能同时兼顾速度及灵活性。高层运算的特点是所处理的数据量较底层少,但算法结构复杂,适宜采用运算速度高、寻址方式灵活、通信能力强的DSP芯片来实现。

DSP+FPGA结构最大的特点是结构灵活,有较强的通用性,适用于模块化设计,从而能够提高运算、处理的效率;同时开发周期短,易于维护和扩展,适于实时图像处理,对不同算法有较强的适应能力。

硬件结构设计

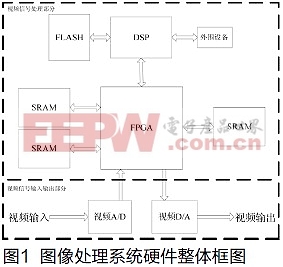

如图1所示,实时图像处理系统硬件设计可分为视频信号处理部分和视频信号输入输出部分。首先通过视频A/D接收前端PAL制式模拟视频信号,经过处理转换后输出数字视频信号。通过FPGA的时序控制将数字视频信号存储到SRAM中。然后利用DSP对SRAM中图像数据的采集、运算和处理,提取出有用的信息,最后将处理完成后的图像数据通过FPGA的时序控制,整合成数字视频信号输出给视频D/A,转换成PAL制式模拟视频信号输出。

视频信号输入输出部分主要由视频A/D和视频D/A组成。

视频A/D采用ADI公司的10位高性能ADV7180,它具有三路模拟视频通道,支持多种制式视频信号输入,输出标准ITU656 4:2:2格式数字视频信号。ADV7180还提供行、场同步信号和27MHz像素时钟信号,省掉了时钟同步电路的设计,为系统设计带来了方便。内置的I2C接口提供了对芯片内部电路的控制功能。可实现对输入视频信号的预处理,比如对比度和亮度的控制、输出数据格式的选择控制等。FPGA控制数据传输的时序,同时根据行、场同步信号,为SRAM提供地址信号和片选、读写等控制信号,将图像数据存入SRAM中。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)