基于FPGA芯片的GPS信号源的设计方案介绍

频率合成器是发射系统和接收系统中的核心器件,采用相位负反馈频率控制技术,具有良好的窄带载波跟踪性能和带宽调制跟踪性能,为系统上、下变频提供本振信号,对相位噪声和杂散具有很好的抑制作用,通过锁相频率合成技术实现的频率源已经在雷达、通信、电子等领域得到了广泛应用。

本文以GPS信号源设计为参考,介绍ADI公司的频率合成器ADF4360-4在GPS信号源设计中的典型应用。

1 信号源系统组成

1.1 系统设计

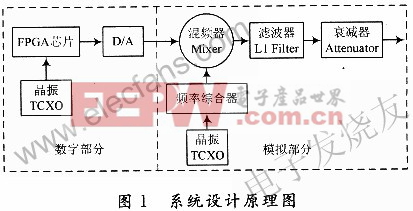

根据文献了解了GPS信号的结构特点,本文设计GPS信号源的目的是模拟卫星发射的GPS信号,也就是对GPS信号进行基带调制并产生频率为1 575.42 MHz的GPS射频信号,根据文献,在系统总体设计中,采用超外差上变频思路,根据系统设计特点,分数字电路和模拟电路两部分,系统设计如图1所示,数字电路部分设计采用软件无线电的思路,利用FPGA芯片完成GPS信号的基带调制和中频调制,输出8 b的GPS数字中频信号,通过D/A器件转换为模拟信号后送到模拟电路;模拟电路部分是整体设计的核心,主要是进行射频电路板的设计与实现,采用频率合成器、混频器等器件,对信号进行混频,滤波,功率控制等,将GPS中频信号混频调制到射频信号,利用射频电路完成上变频功能。

1.2 模块设计

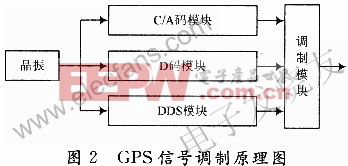

(1)数字电路:数字电路部分就是基带/中频模块设计,采用软件无线电思路,根据文献,利用FPGA芯片产生GPS导航电文(D码)、C/A码、数字中频载波,对它们进行基带调制、扩频调制输出GPS数字中频信号,其中GPS信号调制原理如图2所示,主要由C/A码模块、D码模块、DDS模块和调制模块等组成。其中C/A码模块产生速率l.023MHz的第i颗卫星的C/A码序列,C/A码有1 023个码片,持续周期是1 ms;D码模块产生速率50 Hz的第i颗卫星的导航电文(D码);DDS模块产生速率12.5 MHz的数字载波信号;调制模块对C/A码、D码和载波信号进行扩频调制和BPSK调制,输出12.5 MHz的GPS数字中频信号。

(2)模拟电路:根据文献,模拟电路部分就是射频模块设计,利用频率合成器、混频器、滤波器和衰减器等器件进行射频电路设计,基本原理如图1所示的模拟部分,功能是将GPS信号由中频搬移到射频上,通过滤波器滤波,经可调衰减器调整功率后输出GPS射频信号,完成上变频功能。

2 频率合成器ADF4360-4

2.1 工作原理及其性能

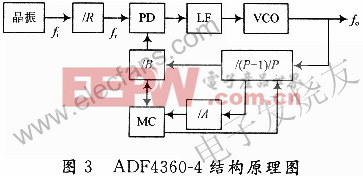

频率合成器主要功能是为系统上下变频提供本振信号,多应用于发射机和接收机系统设计中,通常由数字鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)和可编程计数器(R计数器和N计数器)等组成,数字鉴相器(PD)对R计算器与N计数器的输出信号进行相位比较,得到一个误差电压,经环路滤波器(LF)后控制压控振荡器(VCO)产生所需频率。

频率合成器ADF4360-4是ADI公司生产的高性能锁相频率合成芯片,是一款双模前置分频型单环频率合成器,在不改变频率分辨率时,能有效提高频率合成器的输出频率;其主要性能有,输出频率范围为1450~1750 MHz,可选择二分频,选择二分频时输出信号频率为725~875 MHz;工作电压为3~3.6V;输出信号的功率可控制范围为-13~-4 dBm;可编程双模前置分频器的分频比为8/9,16/17,32/33;能够进行模拟和数字锁定检测;芯片内部集成了VCO等。ADF4360-4的工作原理如图3所示,P/(P+1)为高速双模前置分频器,其分频模数为P+1和P,A为5位脉冲吞咽可编程计数器,B为13位主可编程计数器,R为14位可编程参考分频器,MC为模控制逻辑电路。该器件通过可编程5位A计数器、13位B计数器及双模前置分频器(P/P+1)来共同确定主分频比N(N=BP+A),14位可编程参考R分频器对外部晶振分频后得到参考频率fr=f0/R,因此,设计时只需外加环路滤波器,并选择合适的参考值,可获得稳定的频率输出,其输出频率为f0=fi/R(A+BP),式中,fi为输入频率,由外部晶振提供。

2.2 应用电路设计

在模拟电路射频模块中,频率合成器ADF4360-4为混频器提供本振信号,其应用电路如图4所示,频率合成器的模拟输入是外部温补晶振,晶振通过一个滤波器将标准时钟送到ADF4360-4的16脚REFin;频率合成器的输出管脚是4脚:RFoutA和5脚RFoutB,这两路输出差分高频信号,通过匹配网络和谐振滤波网络送入混频器的差分输入端;第17~19管脚分别是频率合成器初始化时控制数据的CLK脚、DATA脚、LE脚,与测试输出用的20脚MUXOUT一并接到一个5针插头,以便与FPGA芯片连接,作为其输入输出控制接口;12脚Cc为补偿管脚,连一个电容接地;13脚Rset用来设置电荷泵输出最大电流的大小,电流大小由公式ICPmax=11.75/Rest决定,本电路中Rest=4.7 kΩ;14脚CN连一个电容接Vvco去耦;

设计 方案 介绍 信号源 GPS FPGA 芯片 基于 相关文章:

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)