基于单片机的多功能数字钟系统设计与分析

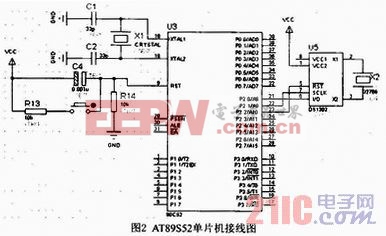

如图2所示,本次设计的多功能数字钟采用一块AT89C52作为主控模块,还用到了转换芯片DS1302,主要是对实现定时电路进行信号交换。在单片机工作之前,我们必须给它一个电源(5V)和连接一些需要连接的地方。比如第18、19引脚之间要给它接上一个12MHz的晶振和两个33pF的电容。第31引脚要接上电源,第9引脚要接上复位电路。第20引脚要接地,第40引脚要接上电源。DS1302芯片主要用于电路的转换。单片机剩下的P0口、P3口、和P2口分别用于其他功能。同时要指出的是在使用P0口时要给它接上上拉电阻,这样单片机的驱动能力就会大大增强。P3口是复用功能,可以用做数据的传输和地址线。特别要强调的是这里只能用高8位做数据线。P2口内部已经具备了上拉电阻,因此不用再加上拉电阻了。这些都是上电之前要做好的一些前提条件,如果忽视了哪一点,都可能使单片机不能正常工作,或者说容易烧坏单片机。

2.2 LCD显示模块电路的设计

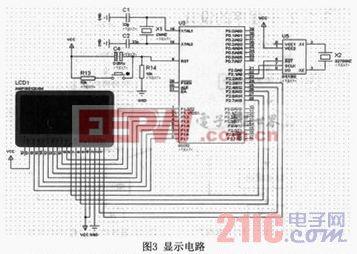

显示电路图如图3所示。从图3中可以观察到,单片机P1口连接LCD的D0-D7, LCD的第1、2脚分别接电源和地,然后由单片机AT89C52载入程序用以控制LCD,由此来显示相应的文字。

为了线路的简便,本显示模块只用到一块LCD(128×64)的液晶显示器。另外,为了使程序更简单,还使用了一块液晶的控制器芯片KS0108来驱动LCD,这样当编写程序时就省去了编写LCD的驱动程序,大大减少了设计的时间段,这样既省时间又不会使电路变复杂。

2.3 闹铃与按键模块电路的设计

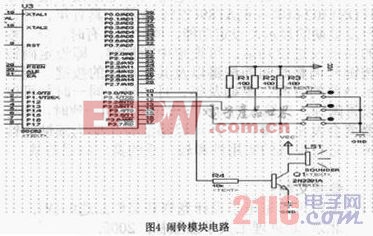

闹铃电路如图4所示。本电路比较简单,只用普通的蜂鸣器接至AT89C52由它进行控制,从图4可以看出单片机P3.0口接喇叭的正极,为了使蜂鸣器的声音大些,P3.0口信号输出端接上一个电阻和一个三极管用于放大声音信号,蜂鸣器的负极直接接地,按键模块用到了三个按钮和三个电阻。单片机的P3.1\P3.2\P3.3与三个按钮相连。按钮的另一端接喇叭的 负极。其中按钮的功能是随时调整时间以及调

整闹钟。

2.4 DS1302时钟模块的设计

2.4.1 引脚功能及结构

图5所示为DS1302的引脚图。其中Vcc1为后备电源,Vcc2为主电源。在主电源关闭的情况下,也能保持时钟的连续运行。DS1302由Vcc1或Vcc2两者中的较大者供电。当Vcc2大于Vcc1正0.2V时,Vcc2给DS1302供电。当Vcc2小于Vcc1时,DS1302由Vcc1供电。X1和X2是振荡源,外接32.768kHz晶振。RST是复位/片选线,通过把RST输入驱动置高电平来启动所有的数据传送。RST输入有两种功能:首先,RST接通控制逻辑,允许地址/命令序列送入移位寄存器;其次,RST提供终止单字节或多字节数据的传送手段。当RST为高电平时,所有的数据传送被初始化,允许对DS1302进行操作。如果在传送过程中RST置为低电平,则会终止此次数据传送,I/O引脚变为高阻态。上电运行时,在Vcc大于或等于2.5V之前,RST必须保持低电平。只有在SCLK为低电平时,才能将RST置为高电平。I/O为串行数据输入输出端(双向),后面有详细说明。SCLK始终是输入端。

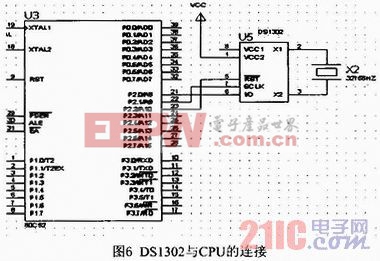

2.4.2 DS1302与CPU的连接

DS1302与CPU的连接电路如图6所示。DS1302与CPU的连接需要三条线,即SCLK(7)、I/O(6)、RST(5)。时钟的显示用LCD。实际上,在调试程序时可以不加电容器,只加一个32.768kHz的晶振即可。只是选择晶振时,不同的晶振,误差也较大(还可以在上面的电路中加入DS18 B20,同时显示实时温度)。只要占用CPU一个口线即可。LCD还可以换成LED,因为LED无法显示较复杂的字符而本设计有用到字符显示,因此系统选用LCD,其特点是可显示任意字段笔划(比如星期)而且显示清晰。

为了初始化任何数据的传输,![]() 引脚信号应由低变高,并且应将具有地址和控制信息的8位数据(控制字节)装入芯片的移位寄存器内,数据的读写可以用单字节或多字节的突发模式方式进行。所有的数据应在时钟的下降沿变化,而在时钟的上升沿,芯片或与之相连的设备进行输入。

引脚信号应由低变高,并且应将具有地址和控制信息的8位数据(控制字节)装入芯片的移位寄存器内,数据的读写可以用单字节或多字节的突发模式方式进行。所有的数据应在时钟的下降沿变化,而在时钟的上升沿,芯片或与之相连的设备进行输入。

3 系统的软件设计

3.1 系统软件概述

3.1.1 DS1302的命令字节

命令字节的格式如图7所示,每次数据的传输都是由命令字节开始的,这里的最高有效位必须是1。D6是RAM(为1)或时钟/日历(为0)的标识位。D1~D5定义片内寄存器的地址。最低有效位(D0)定义了写操作(为0时)或读操作(为1时)。命令字节的传输始终从最低有效位开始。

3.1.2 DS1302的控制字节

DS1302的控制字节如图7所示。控制字节的最高有效位(位7)必须是逻辑1,如果它为0,则不能把数据写入DS1302中,位6如果为0,则表示存取日历时钟数据,为1表示存取RAM数据;位5至位1指示操作单元的地址;最低有效位(位0)如为0表示要进行写操作,为1表示进行读操作,控制字节总是从最低位开始输出。

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)