P波段小步进频率合成器的研制

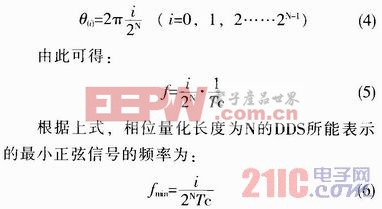

如在系统中采用1000MHz的时钟,需产生的最小正弦信号的频率为0.5MHz,因此,需11位字长的量化就够了。完成了相位量化,再建立起数字相位到数字正弦幅度的映射,然后将数字幅度变成模拟波彤,就能直接输出正弦信号了。

2.2 锁相模块设计

这部分是整个频率综合器的核心,它以10MHz为频率步进产生我们所需的射频信号,并在环路内实现了调频,频率捷变直接VCO等功能。

QPE3336集成了VCO分频,参考分频和鉴相等功能,它的VCO输入信号频率的典型值可达3GHz,它具有高的鉴相增益,Kφ=0.403V/Rad,低的相噪基底,可达-150dBc/Hz@20kHz,宽的动态范围等特点。它的控制接口采用16位并行总线,均为TTL/CMOS电平,并设有失锁指示,44脚PLCC封装,体积小,是理想的数字锁相环芯片。

PE3336的控制接口包括了4位参考分频值输入R0~R3,12位VCO分频值输入,其中M0~M3,为分频值个位输入,A0~A6,为分频值十位输入,PREEN是控制VCO的分频值是否超过128。

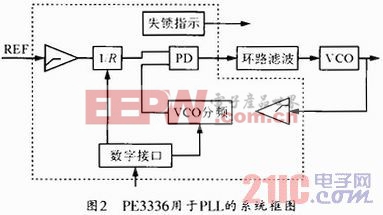

PE3336用于PLL频率综合器的系统框图如图2所示。

用PE3336芯片组成的频率合成器还应包括低通滤波器、压控振荡器等。如图(2)所示,简单介绍如下:

(1)低通滤波器

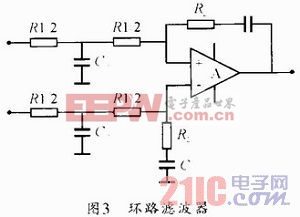

低通滤波器采用有源滤波器,为防止鉴相泄漏,加上了预滤波器,如图3所示。

根据PLL理论可知,R1、R2、C、Cc与环路带宽ωn,环路阻尼因子号,VCO的压控灵敏度KVCO,鉴相增益Kφ,及分频比N的关系有:

环路带宽ωn的选取要综合考虑环路的相位噪声,频率转换时间和运算放大器的工作带宽。在此,我们ωn=300kHz,阻尼因子号取在1~2之间,取定这些参数则有源滤波器的元件参数就可以确定了。

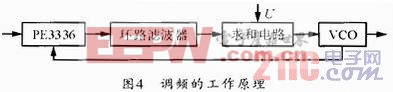

(2)调频工作原理

在PE3336主锁相环内进行调频的工作原理如图4所示。频率调制是由调制信号电压UΩ加在压控振荡器的控制端,利用载波跟踪环而实现的。

由锁相环理论可以知道,为实现线性调频必须使环路等效低通滤波器带宽小于最低调制频率Ωmin,在本系统中调制信号最低频率为200Hz,因此需将原300KHz的环路带宽降到100Hz以下。故采用了一个选择开关,当不调频时环路带宽为300kHz,当选择调频时环路带宽变为100Hz。

3 实验结果

通过对频率源的测试得出如下结论:

频率范围:0.5~1GHz

频率转换时间:

正常工作模式下:6~10μs

直接VCO模式下:≤2μs

置频步长(或频率分辨率):

正常工作模式下:在频率范围内大步进为10MHz~500MHz,

小步进为0.5MHz。

直接VCO模式下:≤1%的波段中心频率

频率稳定度:

正常工作模式下,优于1×10-7/日

直接VCO模式下,优于1×10-5/日

相位噪声: -85dBc/Hz@10KHz~-80dBc/Hz@10kHz

谐波电平抑制:优于-25dBc~30dBc输出功率:10~11dBm

调频功能:具备三角波、正弦波调频,

正弦波调频:调制频率范围:0.1~1MHz调频带宽>100MHz

三角波调频:调制频率范围:200~500Hz调频带宽>100MHz

通过具体测量得出试验数据能满足设计要求有些指标优于设计参数。

4 结束语

现代雷达频率综合器是一门复杂的电子电路技术。技术难度大,因此对设计人员的设计思路、设计基础有较高的要求。国内雷达整机单位均在研制雷达频率综合器。但大多数是采用直接式频率和成方案。而间接式频率综合器也有其自身的优势,从体积、成本等方面还有潜力可挖。因受到器件及设计思路的和结构方面的原因,国内的频率综合器与国外的相比还有一定差距。为此我们还要进行,更细致、深入的研究,力争赶超国际先进水平。

- AT89C2051控制LMX2332的频率合成器(10-15)

- 关于FPGA的跳频通信频率合成器设计(11-07)

- 单片机控制的ADF4106锁相频率合成器设计(09-29)

- 基于AD9911频率源的设计与实现(10-15)

- 21篇利用DDS进行频率源、信号源、及其他设计技术文献(04-21)

- Windows CE 进程、线程和内存管理(11-09)