基于SOPC 的嵌入式Web 服务器设计与实现

摘要:设计并实现了基于SOPC技术的嵌入式Web服务器,简单介绍了SOPC技术的特点及构建方法,随后对该嵌入式Web服务器的实现在硬件和软件两方面都作了详细论述,其中运用Nios II软核处理器作为主控制器,实时多任务操作系统uC/OS-II为应用软件运行平台,简化的TCP/ IP 协议LwIP为应用层通信协议。具有设计灵活、可重构、集成度高、实现风险低、开发周期短的优点。

1、引言

近来,随着嵌入式Internet技术的飞速发展,当今社会逐渐步入网络时代。嵌入式Web服务器技术在远程监控和生产过程控制系统中得到了广泛的应用,该技术允许任意地点的用户通过Web浏览器接入网络,访问Web服务器发布的各类信息,通过Web可以实现最为亲切的信息互动。

基于SOPC(可编程片上系统)技术的嵌入式Web服务器采用嵌入式软核处理器技术,使用嵌入式实时操作系统,内嵌网络接口和网络通信协议,可直接接入以太网。由于嵌入式Web服务器具有成本低、体积小、高可靠、微功耗、环境适应能力强等诸多优势,在通信和工业控制等领域正得到日益广泛的应用。

2、Web服务器概述

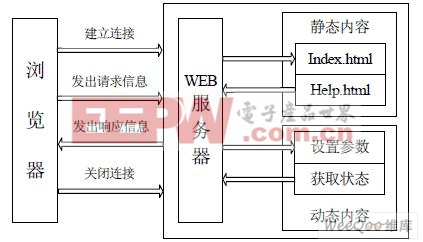

本设计介绍的嵌入式Web服务器采用基于FPGA的Nios II 软核处理器,具有灵活性高、而成本低的特点,充分体现了可编程片上系统的优势。客户端通过IE浏览器对该服务器进行访问,实时地获得服务器发布的各类信息,以便执行相应的操作。这样就要求服务器提供WWW服务,即实现HTTP协议。它应被所有浏览器支持,以保证任何地方的用户都可以通过浏览器下达命令。在网络接口上,本设计选择以太网为其运行的网络环境。如图1所示为HTTP设计模型[1]。首先,客户端的浏览器与Web服务器使用一个或多个TCP连接,通过80号端口进行通信,浏览器通过HTTP协议浏览存储在FLASH中的网页,通过该网页传递浏览、控制命令到网络服务器,然后服务器对命令进行解析,调用相应的功能,充分实现客户端与浏览器之间的信息互动。根据Web服务器的原理,本设计实现了以下协议:DHCP、HTTP、TCP、IP、ICMP、ARP。

3、硬件结构设计

3.1、FPGA芯片

服务器的整体硬件方案采用1 片规模较大的FPGA 完成大部分功能,该款FPGA采用Altera公司的低价格、高性能的Cyclone系列,根据系统逻辑规模的预判,选EP1C20F400C7不胜数FPGA。此型FPGA含有以下可编程逻辑资源:20 060个逻辑单元;64个M4K RAM块,多达294 912位RAM;内嵌2个PLL(锁相环),可作为全局时钟;最大用户I/O引脚301个;且该芯片还支持用Altera公司的SOPC Builder工具嵌入Nios II的内核。

图1 HTTP设计模型

3.2、Nios II 软核处理器

Nios II[2]是在Altera公司的FPGA上实现的一款嵌入式处理器。Nios II系列嵌入式处理器是一款用户可配置的通用的32/16位RISC(精简指令集)结构的CPU ,它定位于广泛的嵌入式应用。使用业界领先的设计软件Altera 公司的Quartus II软件以及SOPC Builder 工具。

3.2、Nios II 软核处理器的实现与应用

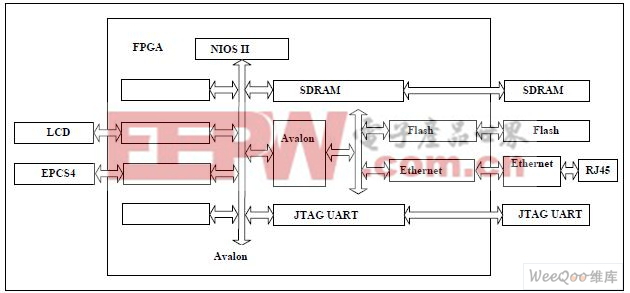

系统采用32 位嵌入式Nios II软核,它可以提供灵活丰富的接口,针对该系统的需求配置合适的外围设备。在Altera 公司提供的SOPC软件中对该软核进行配置时,我们选用了NIOSCPU、内部定时器、JTAG异步串行接口、SDRAM 控制器、Flash 存储器接口、以太网接口、LCD接口、片内存储器和EPCS4串行配置器件控制器接口。其框图如图2所示。

图2 SOPC系统硬件实现框图

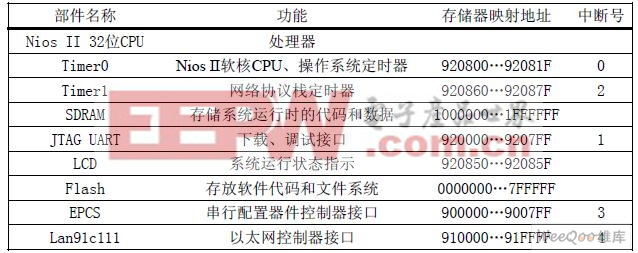

在SOPC芯片中,所有部件都由Altera 公司或第三方以IP 核的方式提供,可方便复用,用户也可在FPGA 中自定义用户模块,并生成自定义IP(知识产权)核。系统部件及其功能见表1。CPU 和所有部件通过Avalon 总线连接在一起,构成基于Avalon 总线的SOPC 系统架构。

Avalon总线是Altera 公司开发的片上总线,是一种简单的总线体系结构,用来将处理器和周边设备集成到SOPC 中,并规定了主设备和从设备的端口连接方式和时序关系。主设备和从设备的交互采用“从端仲裁”技术。在多个主设备试图访问同一个从设备时,用于决定哪个主设备获得访问权。在本文的系统设计中,CPU 是主设备,其他部件均为从设备。

表1 SoPC 中的系统部件

4、SOPC的构建方法

SoPC 系统的设计基于EDA 工具的可编程逻辑器件设计流程,是一个软/ 硬件协同设计的过程[3]。采用Altera 公司SOPC Builder 设计工具,可以极大提高系统得设计效率,开创了嵌入式系统设计的新理念。

硬件开发流程:用 SOPC Builder 系统综合软件来选取合适的CPU、存储器以及外围器件,并定制它们的功能。使用Quartus II 软件来选取具体的Altera 可编程器件系列,并对SOPC Builder 生成的HDL 设计文件进行布局布线;在使用Quartus I

设计 实现 服务器 Web SOPC 嵌入式 基于 相关文章:

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)