基于高分辨率乘法DAC的交流信号处理简介

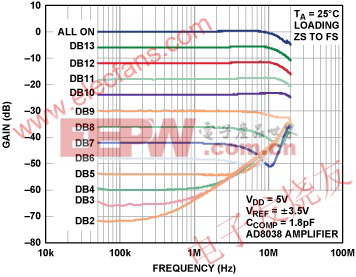

直到最低有效位DB0,每下降一位,增益便降低6 dB(图 8)。不过,对于较低的位,容性馈通影响增益的频率更高。这一点从较低位尾部上翘的平坦曲线可以看出。例如,14位DAC的DB2处,所有频率的理想增益应为–72 dB,但由于馈通效应,1MHz时的实际增益为–66 dB。

图 8. 乘法馈通误差

选择正确的运算放大器

乘法DAC电路性能非常依赖于所选运算放大器的能力,从而在电阻梯输出端保持零电压,并实现电流电压转换。要实现最佳的直流精度,重要的是要选择具有低失调电压和偏置电流的运算放大器,以保持误差与DAC的分辨率相当。详细的运算放大器技术规格参见器件数据手册。

对于基准电压输入为较高速信号的应用,需要一个带宽较宽、压摆率较高的运算放大器,以免削弱信号。一个运算放大器电路的增益-带宽受反馈网络的阻抗水平和增益配置限制。要确定所需的GBW,一种可行的方式是选择–3 dB带宽(10 倍于基准信号频率)的运算放大器。

必须考虑运算放大器的压摆率规格,以限制高频大信号的失真。对于AD54xx和AD55xx系列,压摆率为100 V/µs的运算放大器一般就够了。

表 1 列出了可供乘法应用选择的运算放大器。

表 1. 适用的 ADI 公司高速运算放大器

| 产品型号 | 电源电压 | BW (–3-dB) | 压摆率 | 最大VOS | 最大IB | 封装 |

| AD8065 | 5 至 24 | 145 | 180 | 1500 | 0.006 | SOIC-8, SOT-23-5 |

| AD8066 | 5 至 24 | 145 | 180 | 1500 | 0.006 | SOIC-8, MSOP-8 |

| AD8021 | 5 至 24 | 490 | 120 | 1000 | 10,500 | SOIC-8, MSOP-8 |

| AD8038 | 3 至 12 | 350 | 425 | 3000 | 750 | SOIC-8, SC70-5 |

| ADA4899 | 5 至 12 | 600 | 310 | 35 | 100 | LFCSP-8, SOIC-8 |

| AD8057 | 3 至 12 | 325 | 1000 | 5000 | 500 | SOT-23-5, SOIC-8 |

| AD8058 | 3 至 12 | 325 | 850 | 5000 | 500 | SOIC-8, MSOP-8 |

| AD8061 | 2.7 至 8 | 320 | 650 | 6000 | 350 | SOT-23-5, SOIC-8 |

| AD8062 | 2.7 至 8 | 320 | 650 | 6000 | 350 | SOIC-8, MSOP-8 |

| AD9631 | ±3 至 ±6 | 320 | 1300 | 10,000 | 7000 | SOIC-8, PDIP-8 |

结论

自首款CMOS M-DAC问世以来的近40年间,相关器件不断更新换代,许多新的功能特性层出不穷,性能持续提升,成本和尺寸则大幅缩减。我们的高分辨率、14位/16位电流输出DAC产品系列AD55xx的最新性能改进

信号处理 简介 交流 DAC 分辨率 乘法 基于 相关文章:

- 用CPLD实现FIR数字滤波器的设计(08-07)

- 基于DSP的短波分集合成接收机(09-01)

- 数字信号处理器TMS320F241在变频空调中的应用(04-28)

- 什么是DSP及DSP技术详解(05-15)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 利用可编程逻辑实现灵活高效的多媒体信号处理(09-14)