如何有效的管理FPGA设计中的时序问题

FPGA的开发系统中,或者我们可以直接将数值复制到FPGA的约束编辑器中。

对于高速存储器接口设计,数据存储器被放置在FPGA装置I/O单元的附近,以尽量减少布线延时的影响。该I/O单元只有一个布线路径为输入数据信号,因此在数据总线的每一部分都存在数据路径延迟。FPGA的PLL也被用来进行适当的时钟控制,并通常有几种可能的从输入焊盘到捕捉寄存器的路径。制造商通过控制特定的属性,使PLL的特点包括相位偏移,相乘,或相除等因素,无论是原始示例的设计代码或约束都可以带入模块。因此,时钟和数据路径的布线和延误必须确定,以实现适当的时钟相位偏移。

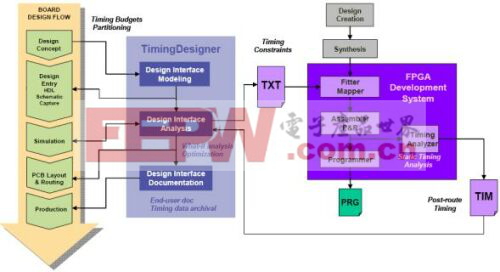

图5:TimingDesigner软件为FPGA设计流程提供直观的界面。

在FPGA的最初布局和布线完成后,时序报告提供数据总线中每个时序的详细延时信息。如果有必要,可为FPGA开发系统的关键信号设定延时路径,TimingDesigner软件可以提取相关信息和利用图表更新。在这个设计实例中,我们需要输入数据总线和相关时钟信号的时序报告。

导入布线后的时序到TimingDesigner软件中

导入FPGA的时序报告信息,我们需要规划最坏的情况从而确定在图表(Q_FPGA)中相关的波形图。信号设计规范定义在同一个时序图表中不能带有同名的波形图。通过规划端口, TimingDesigner软件可以过滤时序报告并提取有用的信息。这些规划被存储在图表文件内并可预先解决的布局和布线问题。

提供可视化的捕捉寄存器

从导入时序报告文件开始, TimingDesigner软件为关键信号延时创建变量,并在电子数据表中规划和分配这些信号端口。变量过去是用来在时序图中更新时钟与数据关系。现在,可确定在FPGA器件内捕捉寄存器中的边缘关系。

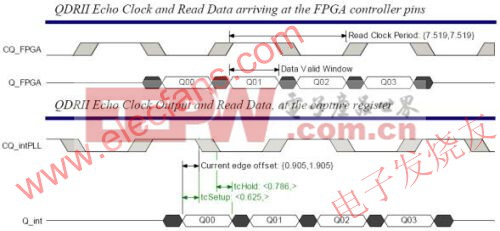

内部寄存器建立和保持是从时序报告和相关的约束中提取所需的时序。下一步,在时序图表中添加另外两个信号和偏移时序报告中的布线延时;在捕捉寄存器中添加数据和时钟,然后建立和保持FPGA器件适用的约束。用时钟边缘和有效数据窗口边缘的补偿确定必要的相位偏移,来平衡设计中有效的数据窗口。

平衡有效数据窗口

我们可以使用下列公式来确定PLL时钟信号产生的相位偏移:

1、从设计的实际有效数据窗口减少FPGA装置I/O部分的最小有效数据窗口,然后结果除于2,实际结果为这2个有效数据窗口的差额(DlyDVW)。(参考图3)

DlyDVW=(DVWdata-DVWdev)/2

2、I/O寄存器数据建立时间加上DlyDVW值,就确定了相对时钟边缘的有效数据窗口(DlyRelSU)。

DlyRelSU=DlyDVW+IOEsu

3、最后,从相对建立时间(上面第2步得到的数值),减去时钟信号与捕捉寄存器的有效数据窗口(从时序图测量)之间的补偿。

Clk_offset=DlyRelSU-EdgeOffset

利用上述公式,我们可以确定FPGA开发系统中PLL的相位偏移量,并执行到下一步的布局和布线。

验证结果

再次导入做过以上修改的布线后时序文件,TimingDesigner软件会自动更新需要的数值,并更正及重新定位I/O单元的时钟信号CQ_intPLL。如图6所示。依靠改变PLL,确切的平衡建立和保持空余将是不可能的。对于这些情况下,应该在FPGA装置的PLL中获取平衡增量以解决这个问题。

图6:在改变时钟和平衡建立及保持空余后,获取数据分析的时序图表。

五、综述

高速设计往往有严格的规范和严谨的发布时间表,所以需要一个交互式的时序规划和分析工具,来获得快速和完整的时序空余,以分析并解决可能影响到最终设计成功的因素。本文说明了如何利用TimingDesigner软件对FPGA设计流程进行准确地捕捉和交换时序信息,以帮助在整个设计过程中管理时序空余,并提供可视化的界面验证设计,并预测设计性能。今天的FPGA器件产品都带有多功能的时钟配置和丰富的I/O资源,并且带有高数据传输能力,TimingDesigner软件为高速存储器如DDR QDR SRAM提供精确的关键路径时序分析功能。

- CPLD在DSP系统中的应用设计(04-11)

- 基于C语言的I2C总线软件模块设计(01-09)

- Verilog HDL基础之:时序逻辑电路(06-05)

- FPGA系统设计的仿真验证之: 功能仿真和时序仿真的区别和实现方法(06-05)

- 基于CPLD及钨铼热电偶温度传感器的爆炸场温度动态测试(06-05)

- SOC时序分析中的跳变点分析(06-05)