基于DSP的嵌入式数字摄像夜间能见度测量系统

摘要:数字摄像夜间能见度仪的关键技术之一在于高速、实时地处理CCD采集的目标光源和黑体的图像信息。设计了一种基于TMS320DM642的小型化、便携嵌入式能见度测量系统,从硬件和软件上给于实现,并将其应用到数字摄像夜间能见度测量中。利用CCD采集25帧/s的PAL制视频流,数字化后送入DSP处理器,通过DSP实现目标光源与黑体的图像分割与定位算法,完成数字摄像夜间能见度的测量。实验结果表明设计的嵌入式系统能较好完成夜间能见度的测量。

关键词:DSP;图像处理;夜间能见度;嵌入式系统

0 引言

能见度是气象观测中的重要参数,其对于航空航天、铁路、公路等具有重要的应用价值。数字摄像法是根据能见度定义以及人眼视觉阈值效应自动获得能见度值的,是一种较为新型的探测能见度的方法。其基本思路是通过直接处理摄像机(CCD)摄取的选定目标物的图像,分析亮度信息来获得能见度数值。文章研究了双光源摄像法夜间能见度测量方法,设计了基于DSP的小型化嵌入式系统,从硬件和软件设计两方面

对系统进行了研究,实现了夜间能见度的计算。实验结果表明该系统可以用于夜间能见度的观测。

1 数字摄像法探测夜间能见度原理

采用双光源法开展夜间能见度探测的原理如图1所示。

分别为光源1,2,黑体1,2的视亮度;D1和D2分别为光源1,2距摄像机的距离。

再根据人眼视觉阈值效应得到能见度值为D=ln(1/0.02)/σ。

2 嵌入式系统硬件设计

2.1 系统总体方案设计

系统其主要由目标光源与黑体、摄像机和信号处理平台组成。信号处理平台完成信号的图像采集、分割与能见度计算功能。本文设计了一套以TMS320DM642为核心,结合CY37064P100,TVP5150PBS,SAA7121,DMT32240T035_01WN的图像实时采集与处理平台。该平台完成图像的采集与分割定位的处理,目标光源与目标黑体的视亮度以及能见度值的计算。图2为系统模块结构图。

采用PAL制式的摄像头提供25帧/s的视频流。CCD采集图像并通过视频解码芯片将输入视频流转化为8位ITU-R BT.656格式视频数据,经过DSP图像处理得到能见度的数值。再通过DM642扩展的串口通信电路与带串口的液晶屏通信,把能见度数值显示在液晶屏上。同时视频编码芯片将DSP处理后的BT.656格式的视频数据转化为PAL制式的视频信号,通过监视器显示处理后的目标光源和目标黑体的图像。

2.2 嵌入式信号处理系统硬件设计

2.2.1 视频采集模块

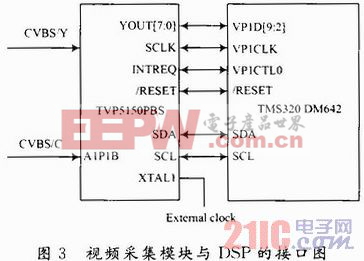

采用8位模拟工业摄像机直接摄取PAL制的视频图像,送入视频解码器。解码后输出ITU-R BT.656格式数据。解码器采用高性能、封装小(32脚TQFP)、功耗小(小于150 mW)的TVP5150PBS,将PAL视频信号转换成数字色差信号(YUV 4:2:2)。图3为视频解码模块与DSP接口图。

在外部视频输入(0~1 Vpp)与TVP5150PBS视频输入之间设计分压电阻网络来使得TVP5150PBS的输入电平为0~0.75 Vpp。

系统设置视频口VP1的A通道作为视频输入口。TMS320DM642的I2C接口实现对TVP5150芯片内部寄存器的初始化和配置。TVP5150芯片的SCL,SDA引脚分别与TMS320DM642时钟、数据地址线相连,通过SCL,SDA的时序配合完成DSP向视频解码器芯片寄存器写入和读出数据。TVP5 150接收摄像机的视频信息,经过解码后的数据串行输出。数字视频流包含奇偶场指示信号FI、场同步信号、行同步信号、像素时钟、YUV数据输出等元素,数据率约165 Mb/s。

2.2.2 图像处理模块

系统采用TI公司的面向数字媒体应用的32位定点DSP芯片TMS320DM642完成信号处理的过程。TVP5150输出的BT.656视频流经过TMS320DM 642的视频口后存入2 560 B的VP1A通道FIFO。由于图像数据量大,需要外扩片外存储器用于存放图像数据信息。通过EDMA通道把FIFO中的数据搬入片外存储器SDRAM。当视频口VP1的A通道出现视频Y,U,V分量数据搬运请求后,在程序中便会触发EDMA处理函数,完成FIFO数据向SDRAM的搬运。VP1EVTYA,VP1EVTUA,VP1EVTVA分别为发生在VP1A通道上与视频Y,U,V分量相关的事件,与DM642 EDMA对应通道相连。当FIFO向SDRAM搬运完数据后运行在FLASH中的程序开始调用图像数据,进行算法处理,求取光源和黑体的亮度值,完成能见度的计算。

2.2.3 视频显示模块

视频显示部分通过视频编码芯片把BT.656格式的视频数据转化为PAL制式的视频信号,然后送入监视器显示处理后的目标光源和目标黑体图像。采用SAA7121H编码器,将TMS320DM642的VP0 A通道设置为视频输出口。图4为视频编码模块与DSP连接图,CVBS_OUT为解码输出的复合视频。与TVP5150一样,SAA7121芯片内部各个寄存器的配置通过TMS320DM642的I2C接口配置,且可以与TVP5150共用TMS320DM642的I2C总线。

能见度 测量 系统 夜间 摄像 DSP 嵌入式 数字 基于 相关文章:

- 基于DSP的光纤高温测量仪的软件设计 (04-08)

- 基于DSP处理器的光纤高温测量仪的设计方案(05-08)

- 用DSP实现抖动(Jitter)测量的方法(04-28)

- 基于dsPIC30F2010的土壤水分测量仪的设计研究(08-27)

- 用DSP实现增量式光电编码器的细分(01-01)

- MSP430在电力测控保护产品中的应用(01-15)