基于Q-Coder算术编码器的IP核设计与仿真

时间:09-23

来源:互联网

点击:

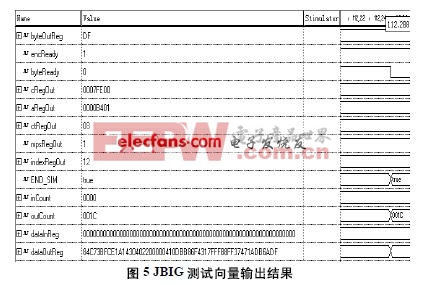

有验证算术编码器编码正确性的测试向量,因此该测试向量被用以测试本文设计IP核的正确性。需要说明的是:JBIG标准中的算术编码器会产生“FF AC”标志位[8],而JPEG2000中的MQ-Coder算术编码器并不产生该标志位[1]。 将JBIG中的测试向量作为输入,经过本文设计的算术编码IP核处理后的结果如图5所示,由图5可知本文设计的算术编码IP核完全正确。 (3)由概述可知,Jasper软件具有一定的权威性,因此在实验中被使用。表1列出了对于同一个图像文件,Jasper软件中算术编码模块执行所需的时间和本文设计的算术编码IP核执行所需的时间以及两者时间之比。 5 结论 本文提出的一种实现算术编码的集成电路IP核,经过仿真和FPGA验证,能够符合JPEG2000标准,仿真结果表明,在相同的条件下,该IP核编码所需时间仅约为软件编码所需时间的40%,从而大大提高了算术编码的效率,使得将来其应用于实时处理系统成为可能;并且将来可以定制所需的ASIC电路,用于新一代数字照相机等具有广泛市场前景的项目。

设计 仿真 IP 编码器 Q-Coder 算术 基于 相关文章:

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)