一种基于PCI总线的反射内存卡系统设计

对实时传输, 传统的以太网络由于传输协议开销的不确定性, 很难满足实时网络的要求, 实时网络是一种应用于高实时性要求的专用网络通信技术, 一般采用基于高速网络的共享存储器技术实现。除了具有严格传输确定性和可预测性外, 还具有传输速度高、通讯协议简单、软硬件平台适应性强、可靠的传输纠错能力、支持中断信号的传输等特点。鉴于以上原因, 设计一款反射内存卡, 写入一个节点的内存的数据可以通过网络硬件传输到其它所有的节点。

2 硬件设计

反射内存卡系统的总体框图如图1 所示, 主要由5部分组成:FPGA、PCI 接口、SDRAM、数据编解码电路、光纤收发电路。

其中,FPGA 内部包含SDRAM控制器和FIFO 控制器、编解码控制器、接收FIFO、发送FIFO、中断FIFO及中断控制等。FPGA 选用Cyclone II 系列的EP2C35F484C7;PCI 选用PLX 公司的PCI9054,能够提供两个独立的DMA 引擎,每个都可以进行读写,在一个DMA 读取数据的同时另一个DMA 可以写入数据,加快系统工作速度; 编解码芯片选用安捷伦的H D M P -1636A,提供十位的并行IO,串行数据传输速率达1062.5MBd,负责数据串并行和并串行转换,以便与光纤收发器内部数据格式进行匹配; 光纤收发器选用安捷伦的HFBR-57L5AP,支持多模光纤,串行传输速率达1.0625Gb/s,负责将电信号转化为光信号, 通过光纤向下一节点传输。

图1 反射内存卡系统的总体框图

2.1 SDRAM 控制器

与双端口RAM 相比,SDRAM 容量大、价格低,采用128M 的SDRAM 作为反射内存卡的数据存储器。由于SDRAM 读写不能同时进行,且需要刷新维护,因此,需要设计SDRAM 控制器。

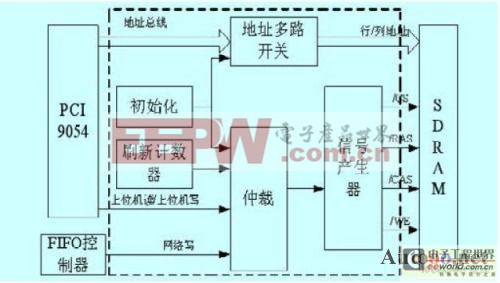

SDRAM 控制器实现对SDRAM 的读写控制与仲裁,提供类似于双端口RAM 的外部接口。SDRAM 控制器内部由初始化模块、刷新计数器、地址多路开关、仲裁及信号产生器等组成,SDRAM 控制器结构如图2 所示。

图2 SDRAM 控制器结构图

SDRAM 控制器内部各模块功能如下:

(1) 初始化模块在上电之后对SDRAM 的模式寄存器进行设置;(2) 刷新计数器对SDRAM 进行定时刷新;(3) 地址多路开关将地址总线上的地址转化为SDRAM 的行列地址;(4) 仲裁机构要对上位机读、上位机写、网络写和刷新等操作做出仲裁。当读写和刷新同时产生时, 先完成相应的读写操作然后再刷新, 而上位机读、上位机写、网络写这三种操作的优先级从高到低依次是网络写、上位机读、上位机写;(5) 信号产生器根据不同的读写操作产生不同的读写信号, 从而SDRAM 可以正常工作, 而不发生读写冲突。

2.2 FIFO 控制器

在峰值速率下进行数据传输,SDRAM 存储器很难达到要求,所以使数据经过FIFO 缓存后发送或接收,可以降低了对存储器传输速率的要求, 实现较高的传输速率。设计了FIFO 控制器,它由数据解析、数据封装、仲裁、读信号产生器、写信号产生器组成。FIFO 控制器结构如图3 所示。

图3 FIFO 控制器结构图

FIFO 控制器内部各模块功能如下:

(1) 数据解析对从网络中接收的数据进行判断,如果是中断事件将中断数据写到中断FIFO 中,如果是需要共享的数据则一部分送到SDRAM 控制器,一部分送仲裁机构;(2) 数据封装对本节点发送的数据重新打包,加入数据类型、数据包长度、发送节点ID、目标节点ID 及校验等相关信息,以便于其他节点对数据进行解析;(3) 仲裁机构对来自接收FIFO 的数据和本节点发送到数据进行仲裁, 当他们同时到达时来自接收FIFO的数据优先;(4) 读信号产生器在接收到半满中断时产生读信号,从接收FIFO 中读出相应的数据,避免FIFO 充满或溢出;(5) 写信号产生器在仲裁机构向下发送数据时给发送FIFO一个写信号。FIFO控制器仿真时序如图4所示。

图4 FIFIO 控制器仿真时序

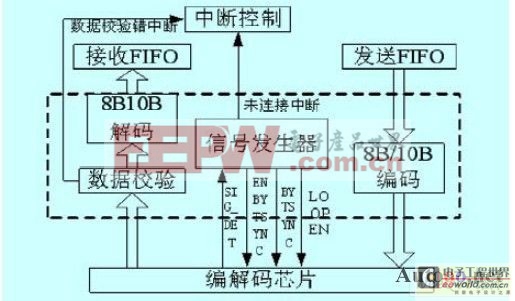

2.3 编解码控制器编解码控制器由信号产生器、数据校验、8B/10B编码、8B/10B 解码组成。编解码控制器结构如图5 所示。在这部分主要是进行数据8B/10B 编解码,以与编解码芯片数据格式匹配同时给编解码芯片的正常工作提供控制信号,数据编解码控制器仿真时序如图6 所示。

图5 编解码控制器结构图

图6 数据编解码仿真时序

3 软件设计

软件设计包括驱动程序和应用程序两部分。驱动程序提供的API 接口主要包含以下四个方面的功能: 打开和关闭驱动、配置反射内存卡、数据传输、中断控制与处理。当应用程序访问反射内存卡资源时,反射内存板必须打开, 一个句柄将返回到应用程序。图7是应用程序处理的流程图。

图7 应用程序流程图

4 性能测试

用三块反射内存卡组成环形反射内存网, 由节点1向2 节点发送数据, 节点2 发送到节点3, 由节点3 向节点1 发送确认中断,

- 用双端口RAM实现与PCI总线接口的数据通讯(05-06)

- 基于PCI总线和DSP芯片的图像处理平台的硬件设计(07-06)

- 基于DSP和PCI总线的通用数字信号处理系统(11-13)

- 一种基于PCI总线和DSP技术的虚拟仪器设计(03-16)

- 基于Linux平台的天气雷达高速数据采集系统设计(03-13)

- 基于DSP与PC机的PCI总线高速数据传输 (07-08)