使用PLD和低开销的串行总线扩展系统控制功能

微控制器通信。然而,它也负责执行线路上额外的监测/控制分析和故障信息记录,通过串行总线写入非易失性存储器。电压监控、看门狗定时器和PCB上的其他故障条件可以通过PLD写入非易失性存储器。通常情况下,检测到故障后,系统中其他监控器的状态,如温度和电压以及时间信息将被保存。

应当注意的是,这样一个系统在实现时有一个重要的考虑。如果PLD是外部非易失性存储器的主器件,那么它还需要决定串行总线的控制和寻址。这个决定对于使用SPI总线而言很容易;设计师必须实现一个从SPI器件,与微控制器进行通信,以及一个独立的主SPI器件,可以访问外部存储器。

对于I2C总线,设计师有几个选择。第一种选择是设计类似SPI那样的设计,使用一个从器件与微控制器通信,以及一个主器件访问外部存储器。第二种选择是使用PLD,同时作为主器件和从器件。这种方法的好处是,系统中只有一条串行总线,因此微控制器可以直接访问非易失性存储器,而无需PLD翻译指令然后从存储器中读取信息。然而,由于不是在PLD中简单地使用一个从器件,现在设计必须处理寻址和总线控制。

传感器和外设汇聚

基于串行接口的标准产品的数量日益增长。你可以在温度传感器、压力传感器、A/D转换器、数字电位器、实时时钟和LCD控制器等等应用中找到串行接口,这里仅列举了几个来说明。要了解如何将这些集成到设计中的关键是要知道哪些外设需要“实时”使用以及“实时”意味着什么。举例来说,在系统中温度是一个相对缓慢变化的对象,并可以很容易地通过串行总线监控。用于电流或电压检测的A/D转换器可能是也可能不是一个“实时”需求,这要根据正在测量的内容,以及需要多快的检测速度而定。

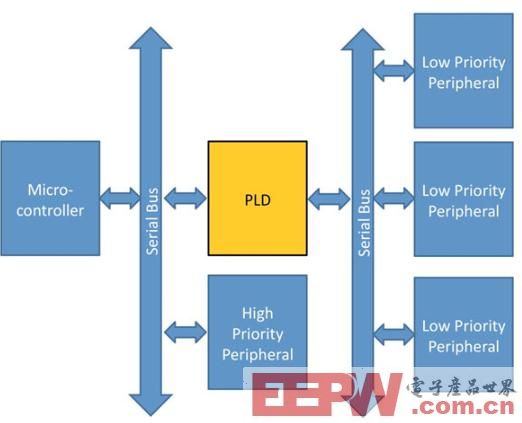

一旦你已经确定了外设的优先级,然后你可以将较低优先级的外设让PLD处理,减轻处理器的负担,如图5所示。

图5——传感器汇聚示例

在上面的例子中,微控制器只需与2个而非4个外设进行通信。

这种安排还有另外一个好处。你可以使用一个功能强大的PLD来预处理数据,然后由微控制器读取。例如,请考虑一个应用,使用A/D采样测量一个三相电力系统的电压和电流,并进行故障检查。一个拥有强大DSP功能的PLD可以代替DSP或微控制器执行RMS计算、峰值电流分析、相位计算和FFT。现在采样速率受到PLD收集样本和处理数据所需时间的限制。然后,微控制器可以读取编译的数据,将更多的时间用于处理控制和报告工作。设计师们应该好好考虑微控制器处理能力、PLD处理能力、成本和空间之间的权衡。

下一步:集成

鉴于这些串行总线与小型可编程逻辑器件相结合使用的实用性,下一步将是将至少一种串行总线标准(如果不能兼顾)集成到PLD中。这种集成降低了PLD解决方案的成本和功耗。此外,串行总线接口的编码不再是设计师需要解决的问题。设计师只需要处理他们的应用和逻辑要求,而不是集成一个开放的核。

莱迪思半导体公司提供的最新的CPLD就可以为设计师带来这些优点。MachXO2™系列中的嵌入式功能块(EFB),包含预先设计的解决方案,可以用来实现上面所述的任意系统控制功能。MachXO2器件包含一个SPI控制器以及2个I2C控制器。所有串行总线控制器都可以配置为主或从器件。此外,MachXO2还为设计师们提供了一个定时器/计数器块以及少量的用户可访问的闪存(UFM)。

除了上面提到的解决方案,串行总线与PLD相结合可以为系统提供其他的好处,即使有时它们在架构设计过程后才显现出来。它们并不是所有弊病的灵丹妙药,但它们在设计中的实用性是有据可查的,有无数的开源核和设计方案可以给予不同的架构设计师们指引,实现最佳的解决方案。

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- 用CPLD实现FIR数字滤波器的设计(08-07)

- 基于DSP+CPLD的交流电机调速在水处理控制中的应用(11-27)

- 一种基于DSP的张力、深度、速度测量系统(04-15)

- 用双端口RAM实现与PCI总线接口的数据通讯(05-06)

- 基于DSP和CPLD的宽带信号源的设计(07-26)