使用FPGA的高动态范围图像信号处理

据来说是必需的。

黑电平校正:每个颜色通道都有一个时间相关的偏移。彩色处理需要线性信号处理,因此所有信号必须没有任何偏移。CMOS图像传感器有所谓暗行输出来衡量每个颜色通道的平均偏移。黑电平校正减去专用彩色通道,基于线路的基准噪声,达到最佳的黑电平结果。

自动曝光:自动曝光模块的目的是要不断调整曝光,以适应实时的不断变化的光线条件。

线性:例如,AptinaMT9Mo24/34 HDR传感器,每颜色通道输出20位信息。为了尽量减少传感器输出的实际线路的数量,Aptina使用智能压缩机制将这一数据压缩到12位。线性化就是将这12位数据解压缩恢复到原来的20位的过程。

缺陷像素校正:由于制造工艺而造成的传感器中死的或热像素,需要使用缺陷像素校正模块进行修正。此模块使用基于相同颜色通道的相邻像素插值法纠正了缺陷的像素值。典型的纠正方法包括冷或热像素检测,使用当前像素邻域中值或平均值估计。

2-D降噪:除冷、热噪点外,传感器像素可以随机成为帧噪声。这意味着它们输出与邻近像素相比过高或过低的强度。基于相同颜色通道的相邻像素的插值法进行2D降噪来纠正噪声像素,与缺陷像素校正模块的工作原理大致类似。

De-Bayering(彩色滤波阵列插值):传感器上的每个像素都有一个所谓的Bayer滤波器,使用三种颜色:红色、绿色或蓝色中的一种。因此,三分之二的色彩数据丢失,由此产生的图像是三种颜色产生的马赛克。要获得一个全彩色图像,各种去马赛克算法,用于为每个像素使用插值算法得到一组完整的红色、绿色和蓝色的值。

色彩校正矩阵(CCM):图像传感器通常提供错误的颜色再现,由于所谓的跨色彩影响,这是由于像素间的信号串扰引起的。这种效应会导致错误颜色的图像(如:偏蓝的绿色)。色彩校正牵涉到复杂的像素数据的矩阵乘法来达到纯正的颜色。

自动白平衡(AWB):传感器不擅长的“识别”色彩。AWB调整图像中的其他颜色,通过所谓的“灰色世界”算法推断出图像中的白色从而进行参考。AWB??通过检查入射光频率(或波长)来确定白色,并呈现自然色彩的图像。

伽玛校正:传感器像素以线性的方式对入射光强度作出反应。为了能够为常见视频系统提供像素数据,如显像管的对数响应,可能需要转化为一个非线性的值编码。伽玛校正提供了这种转换。

高/宽动态范围(HDR/WDR)处理:这就是将20个像素的传感器数据映射为8位RGB数据的模块,从而在显示出来的图像中呈现图像中的明亮和黑暗区域。需要一条宽的内部流水线来确保暗部的细节没有丢失,甚至当侵入者直接将闪光照射到摄像机镜头。HDR与快速自动曝光算法密切配合工作,能在变化的光线条件下迅速调整曝光。

图2 HDR处理后的图像:强闪光从10英寸的距离直接射到镜头,没有造成图像丢失

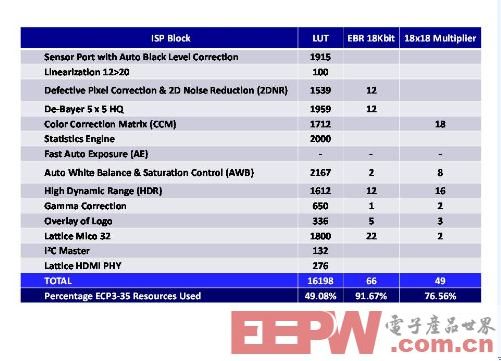

下面表1显示了在33K查找表(KLUT)、低成本、低功耗的FPGA中实现所有上述ISP模块所需的FPGA资源的典型值:

表1 Lattice ECP3-35 FPGA中ISP流水线的FPGA资源使用情况

除了已经提到的ISP模块,实际应用的数据包括统计引擎、生成系统中特定模块使用的图像柱状图、一个Lattice Mico32软处理器用于动态流水线控制、一个I2C主控用于控制各种信号、一个HDMI PHY模块用于直接从FPGA驱动HDMI信号,甚至标志图形的叠加。这说明了可以使用低成本、低功耗的FPGA,如Lattice ECP3-35,来实现整个图像信号处理流水线加上HDMI输出。内部HDR流水线为32位宽,可以提供192dB (20 log 2**32)的高动态范围。在这个实际的应用中,使用具有120dB动态范围的传感器,限制HDR为120dB——仍然是任何FPGA可实现的最高值。实际的应用能够处理每秒60帧的1080p图像,同时提供120dB的高动态范围。

在HDR图像信号处理中使用FPGA的优点

低成本

如上所述,一个简单的低成本33KLUT FPGA可轻松处理一个1080p60流水线。使用Lattice ECP3-35实现的1080p60 HDR摄像机的元器件材料主要包括传感器、FPGA和相关的时钟振荡器、电阻和电容、稳压器、一个HDMI连接器和镜头组装。

高性能

显示的实现提供了120dB的HDR、1080p60性能、业界最快的自动曝光和极高质量的自动白平衡。

低功耗

LatticeECP3与竞争对手FPGA或DSP相比,具有极低的静态和动态功耗。

DDR3支持:FPGA支持DDR3的使用。制造商希望在他们的设计中加入帧缓冲存储器,可以利用这种功能在其摄像机设计中使用高性能、低成本的DDR3存储器。

低功耗的SERDES:一个低功耗具有SERDES功能的FPGA使制造商能够在FPGA中直接实现HDMI PHY,提供HDMI功能,无需增加一块外部HDMI芯片的成本。

综述

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)