一种I2C设备控制方法的设计和实现

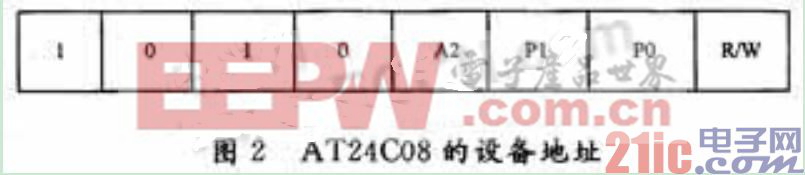

256字节单元,所以若要访问某个单元则需要10位进行寻址,其中最高两位是页地址,低8位是页内地址。设备地址的定义如图2所示,其中P1P0对应页地址,管脚A2可为AT24C08设定两组设备地址。当A2为低电平时,4页的设备地址分别为0A0H,0A2H,0A4H,0A6H;当A2为高电平时;反之为0A8H,0AAH,0ACH,0AEH.因此,为了避免AT24C08与PCF8563的设备地址冲突,需将A2连接高电平。

AT24C08的写操作支持字节写和页面写两种方式。字节写方式中每写一个字节均需主设备提供起始信号、设备地址、内部地址以及停止信号;页面写方式即连续写数据,需主设备提供起始标志、设备地址以及内部地址,数据全部写完后再发送停止标志。

AT24C08的读操作支持当前地址读、随机读和顺序读3种方式。当前地址读表示从当前内部地址单元读出1个字节,所以主设备仅需提供起始信号、设备地址和停止信号;随机读表示从任意内部地址单元读出1个字节,所以主设备需要先提供1次起始信号、设备地址、写操作、设备内部地址和停止信号,设定设备的内部地址,之后再按当前地址读方式读数据即可;顺序读表示从当前地址开始连续读多个字节,所以主设备需提供起始信号、设备地址、读操作,数据全部读完后再发送停止信号。

为了快速读写数据,本文采用页面写的方式将数据写入AT24C08;采用随机读和顺序读相结合的方式读取AT24C08数据。

3 软件设计

3.1 TWI初始化程序的设计

根据TWI的功能特点,TWI初始化的初始化包括以下4步:

(1)配置PIO控制器使复用管脚驱动TWI信号;

(2)配置PMC使TWI时钟处于工作状态;

(3)配置TWI为主工作模式。本文CPU为主设备,日历和存储芯片为从设备;

(4)设置数据传输速率,配置TWI时钟波形发生器寄存器。

3.2 PCF8563驱动程序的设计

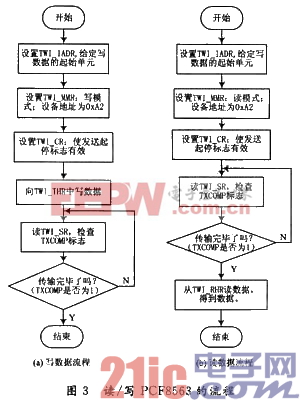

为了控制PCF8563的工作方式,需要对其写入控制字;为了得到PCF8563输出的时间信息,需要对其进行读操作,读/写数据的流程如图3所示。

本文设计编写如下读函数和写函数:

其中,pTwi是结构体指针,指向的结构体中存放TWI的寄存器,通过pTwi即可访问各TWI寄存器;address表示设备地址;im_address表示设备内部地址;data代表读写数据的变量指针。

因此,若使PCF8563工作于普通模式,并读时数据,可用以下代码实现:

3.3 AT24C08驱动程序的设计

由于AT24C08由4个具有不同设备地址的页组成,且采用连续读写数据的操作方式,所以AT24C08的读写与PCF8563读写有以下几点区别。

(1)先设置TWI_CR的起始标志,之后通过TWI_RHR和TWI_THR读/写TWI接口的数据;发送最后一个数据之前,再设置TWI_CR的停止标志。

(2)对于多字节数据的读写,全部数据若没有传输完毕,便不发送停止信号,所以需通过判断TWI_SR寄存器中的TXRDY和RXRDY决定是否读TWI_RHR和写TWI_THR,而将是否出现停止信号作为是否停止发送和接收的判断依据。

(3)由于数据量和起始单元均是随机的,所以有可能出现一页写不下的情况,因此针对给定的数据量和起始单元参数需要计算出共需几页,以便在进行页面切换时更换设备地址。

本文设计编写了如下读函数和写函数。

3.4 软件的调试与运行

本文采用IAR开发环境和J-LINK仿真器进行软件的在线调试和加载运行。调用函数完成以下程序设计:首先从PCF8563连续读出若干数据并写入AT24C08;其次,将AT24C08中的数据读至数组变量中。在程序中的读完AT24C08数据后设置断点,观测数组中存放的数据,从而验证驱动程序的正确性。

4 结 语

本文介绍了PCF8563和AT24C08的使用方法,通过分析基于ARM核的AT91SAM7X256的TWI接口控制方法,设计PCF8563和AT24C08的驱动程序,实现时钟数据的读取和存储。

本文设计的驱动模块已成功地用于智能煤矿分站实验系统中,完成了历史时间数据的记录功能,同时本文为ARM控制多个I2C设备提供了可以借鉴的方法。

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)