UPD78F0411 端口功能

1.1 端口功能

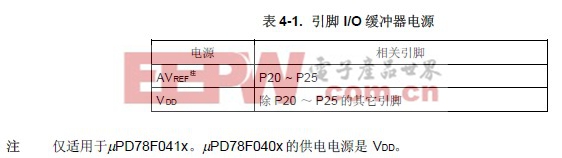

有煞N型的引_I/O _器源:AVREF 注和VDD 。@些源和引_之g的P系@示如下。

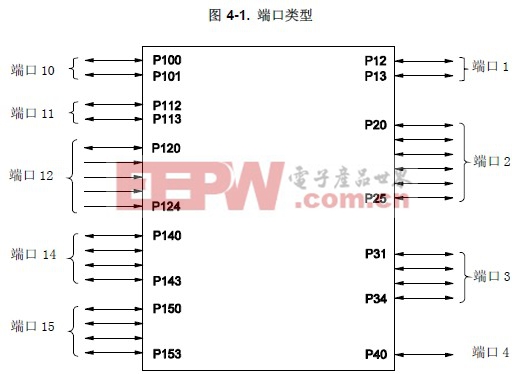

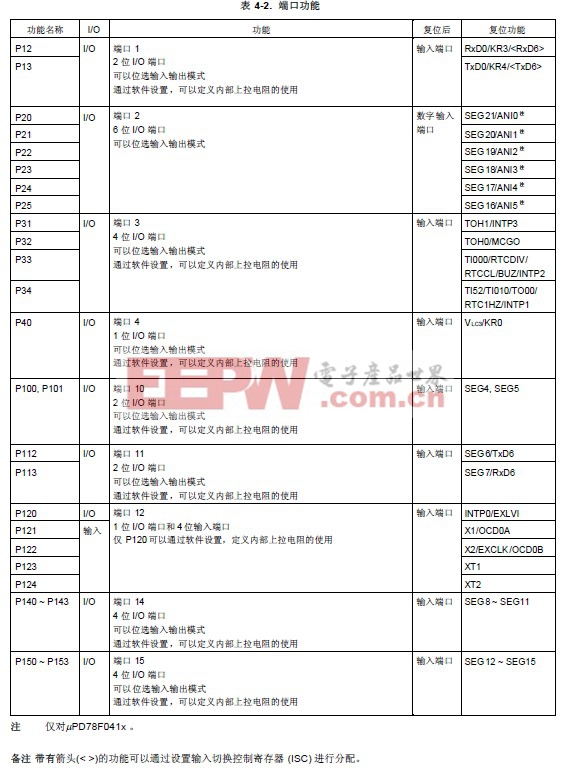

78K0/LC3 b品中提供的端口如D4-1 所示,@些端口可以支持多N控制操作。每端口的功能如表4-2 所示。

除了作底I/O 端口功能,@些端口有}用功能。

1.2 端口配置

端口包括如下硬件。

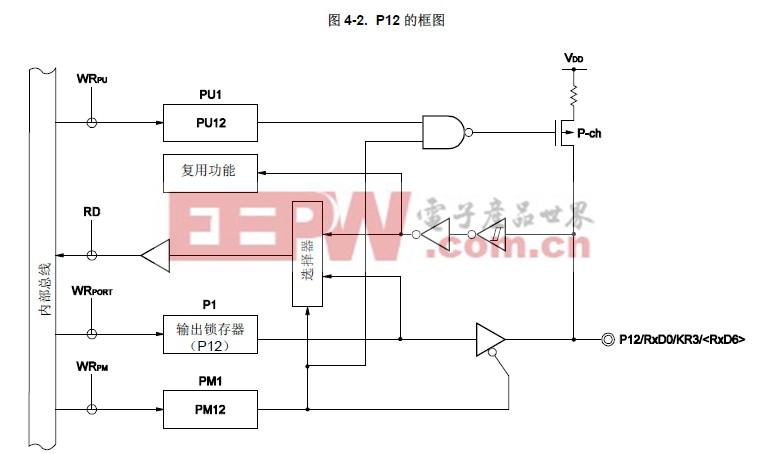

1.2.1 端口1

端口1 是具有出i存功能的2 位I/O 端口。通^使用端口模式寄存器1(PM1),可以位x端口1 入或出模式。如果P12 和P13 作入端口,t内部上拉阻的使用可以通^上拉阻x窦拇嫫1(PU1) 以1 位卧的方式指定。

@端口可以用于按I中噍入和串行接口I/O。

}位信号的b生可将端口1 O置入模式。

D4-2 和4-3 @示端口1 的框D。

P1: 端口寄存器1

PU1: 上拉阻x窦拇嫫1

PM1: 端口模式寄存器1

RD: x信号

WRxx: 信号

P1: 端口寄存器1

PU1: 上拉阻x窦拇嫫1

PM1: 端口模式寄存器1

RD: x信号

WRxx: 信号

1.2.2 端口2

端口2 是具有出i存功能的6 位I/O 端口。通^使用端口模式寄存器2(PM2),可以位x端口2 入或出模

式。

@端口可以用于10 位逐次逼近型A/D DQ器模拟入(HPD78F041x)和segment 出。

P20/SEG21/ANI0 注~ P25/SEG16/ANI5 注,使用端口功能寄存器2 (PF2)O置端口功能(除segment 出) ,使用ADPC0 O置底I/O,使用PM2 O置入模式,将其用作底州入引_。使用@些引_牡臀婚_始。

P20/SEG21/ANI0 注~ P25/SEG16/ANI5 注,使用端口功能寄存器2 (PF2)O置端口功能(除segment 出),使用ADPC0 O置底I/O,使用PM2 O置出模式,将其用作底州出引_。使用@些引_牡臀婚_始。

}位信号的b生可将端口2 O置入模式。

D4-4 @示端口2 的框D。

注 HUPD78F041x 。

P2: 端口寄存器2

PU2: 上拉阻x窦拇嫫2

PM2: 端口模式寄存器2

PF2: 端口功能寄存器2

RD: x信号

WRxx: 信号

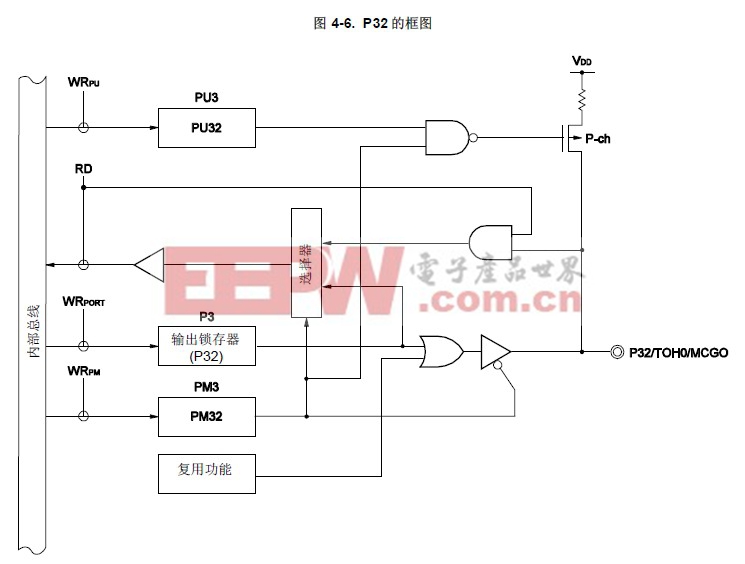

1.2.3 端口3

端口3 是具有出i存功能的4 位I/O 端口。通^使用端口模式寄存器3(PM3),可以位x端口3 入或出模式。如果P31 ~ P34 作入端口,t内部上拉阻的使用可以通^上拉阻x窦拇嫫3(PU3)以1 位卧的方式指定。

@端口可以用于外部中嗾求入、定r器I/O、manchester al生器出、r灯鬏出和蜂Q器出。

}位信号的b生可将端口3 O置入模式。

D4-5 和4-6 @示端口3 的框D。

P3: 端口寄存器3

PU3: 上拉阻x窦拇嫫3

PM3: 端口模式寄存器3

RD: x信号

WRxx: 信号

P3: 端口寄存器3

PU3: 上拉阻x窦拇嫫3

PM3: 端口模式寄存器3

RD: x信号

WRxx: 信号

1.2.4 端口4

端口4 是具有出i存功能的1 位I/O 端口。通^使用端口模式寄存器4(PM4),可以位x端口4 入或出模式。如果P40 作入端口,t内部上拉阻的使用可以通^上拉阻x窦拇嫫4(PU4)以1 位卧的方式指定。

@端口可以用于LCD 与源引_和按I中噍入引_。

}位信号的b生可将端口4 O置入模式。

D4-7 @示端口4 的框D。

P4: 端口寄存器4

PU4: 上拉阻x窦拇嫫4

PM4: 端口模式寄存器4

LCDM: LCD @示模式寄存器

RD: x信号

WRxx: 信号

1.2.5 端口10

端口10 是具有出i存功能的2 位I/O 端口。通^使用端口模式寄存器10(PM10),可以位x端口10 入或出模式。如果P100 ~ P101 作入端口,t内部上拉阻的使用可以通^上拉阻x窦拇嫫10(PU10)以1 位卧的方式指定。

@端口可以用于segment 出。

}位信号的b生可将端口10 O置入模式。

D4-8 @示端口10 的框D。

P10: 端口寄存器10

PU10: 上拉阻x窦拇嫫10

PM10: 端口模式寄存器10

PFALL: 端口功能寄存器ALL

RD: x信号

WRxx: 信号

1.2.6 端口11

端口11 是具有出i存功能的2 位I/O 端口。通^使用端口模式寄存器11(PM11),可以位x端口11 入或出

模式。如果P112 ,P113 作入端口,t内部上拉阻的使用可以通^上拉阻x窦拇嫫11(PU11)以1 位卧的

方式指定。

@端口可以用于segment 出和串行接口I/O。

}位信号的b生可将端口11 O置入模式。

D4-9~4-10 @示端口11 的框D。

P11: 端口寄存器11

PU11: 上拉阻x窦拇嫫11

PM11: 端口模式寄存器11

PFALL: 端口功能寄存器ALL

RD: x信号

WRxx: 信号

P11: 端口寄存器11

PU11: 上拉阻x窦拇嫫11

PM11: 端口模式寄存器11

PFALL: 端口功能寄存器ALL

RD: x信号

WRxx: 信号

1.2.7 端口12

端口12 是具有出i存功能的1 位I/O 端口和4 位入端口。HP120 可以使用端口模式寄存器12(PM12),位x端口入或出模式。如果P120 作入端口,t内部上拉阻的使用可以通^上拉阻x窦拇嫫12(PU12)指定。

@端口可以用于外部中嗾求入、外部低zy的狠入、主系yrR的振器B接、副系yrR的振器B接和主系yrR的外部rR入。

}位信号的b生可将端口12 O置入模式。

D4-11~4-13 @示端口12 的框D。

注意事使用P121 ~ P124 引_B接主系yrR(X1,X2)或副系yrR(XT1,XT2)的振器,或者入主系yrR的外部rR(EXCLK)r,必通^使用rR操作模式x窦拇嫫鳎OSCCTL)X1 振模式、XT1 振模式或者外部rR入模式M行O置(如需了解信息,可⒁5.3 (1) rR操作模式x窦拇嫫鳎OSCCTL)和(3)副系yrR引_操作模式O置)。OSCCTL 的}位值00H(P121 ~P124 都用作入端口引_)。

渥 P121 和P122 能蛴糜谄上{模式O定引_(OCD0A, OCD0B) 。

功能 UPD78F0411 相关文章:

- 基于DSP数字多功能板的实现(09-08)

- 基于DSP2407的多功能电源控制系统设计(09-08)

- DVR操作系统分析(07-23)

- 基于PROTEUS技术的ARM7显示系统设计与仿真实现(11-22)

- 一种大型软件测试方法(08-01)

- 嵌入式软件三大潜在问题及其测试技术(01-13)