基于AD9912镜像频率的应用

摘要:常规DDS频率合成方案无法合成超过1/2采样频率的信号频率,这给DDS器件的应用带来了很大限制。在实际应用中通过对DDS器件的输出信号频谱进行分析发现,其频谱中除包含设计频率以外还包含特高频(UHF)频段的镜像频率分量。计算发现这种镜像频率与合成的设计频率成线性关系,故可通过计算确定镜像频率并通过选频滤波提取它们从而获得UHF信号。为扩展DDS器件的应用范围,提出了利用镜像频率实现UHF频率合成方案,设计了基于AD9912芯片的频率合成系统,编写了相应的控制程序。最终实现了利用DDS器件合成了1 500MHz信号的预想。

关键词:DDS;镜像频率;AD9912;特高频信号

直接数字频率合成即DDS(Direct Digital Synthesis),它将先进的数字信号处理方法引入了信号合成领域理论,实现了合成信号的频率转换速度与频率准确度之间的统一。DDS技术具有输出频率、相位和幅度能够在数字处理器的控制下精确而快速的变换以及能进行极微小的频率调谐和在两个频率间“跳跃”的特点,同时这种技术也具有极好的温度、老化稳定性、转换频率保持相位恒定和小型可靠等优点。因此DDS技术是公认的产生频率的理想方法,是频率合成的第三代方案。八十年代以来各国都在研制和发展各自的DDS产品,如美国QUALCOMM公司的Q233x;STANFORD公司的STEL-1175,STEL-1180;AD公司的AD7008,AD985x等。

近年来随着理论的不断完善和集成工艺的发展,DDS技术已被广泛的应用于雷达、航空航天和通信系统等高端系统中,与此同时DDS器件输出频率受限的缺点也被凸显了出来。而这样的缺点大大限制了DDS技术在UHF频率合成上的应用。因此设计一个合适的频率合成方案来克服这样的不足,是非常必要的。

1 频率合成的基本原理

1.1 DDS设备的基本工作原理

直接数字频率合成器是从相位概念出发根据不同的相位给出不同的电压幅度,即相位-正弦幅度变换,最后滤波,输出所需频率信号。D DS设备主要由相位累加器,波形存储器和数模转换器(DAC)构成。在DDS设备工作时,相位累加器在参考时钟频率的控制下以预先设定好的频率控制字作为步长进行线性累加,得到相位码对波形存储器进行寻址输出幅度码,由DAC转换为阶梯波再经低通滤波器平滑后可以得到相应的合成频率信号。

1.2 镜像频率的产生原理

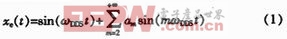

为方便分析,设DDS芯片合成的信号频率为x(t)=sin(ωDDSt),该信号由正弦波离散采样值的数字量经数模转换为阶梯型的模拟波形信号xe(t),其转换关系的数学表达式可以表示为:

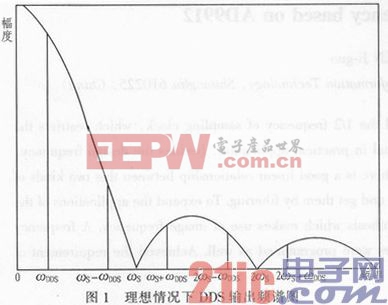

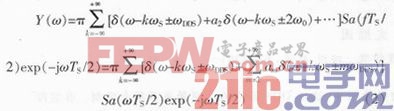

式(1)中的第二项即为各次谐波的分量,其中am表示第m次谐波的幅度。通过采样率为ωs理想采样及理想数模转换(零阶保持的阶梯重构)后的信号频谱Y(ω)可以表示成:

由式(2)可知,输出的信号频谱中除了包含设计频率信号ωDDS及其谐波分量mωDDS,还存在着以采样频率为折叠频率的设计频率的镜像频率,以及设计频率谐波的镜像频率等一系列镜像频率分量。本设计中主要利用的设计频率的镜像频率分量ωm可由式(3)得出:

由于DDS设备的参考频率ωs恒定,nωs可以看做一个常数,由式(3)可知DDS设备最终合成的镜像频率ωm与设计频率ωDDS成1:1的线性关系,设计频率变化量即为镜像频率的变化量,故可通过改变设计频率来精确地控制镜像频率合成。

1.3 AD9912的UHF频合成原理

硬件系统采用AD公司最新的AD9912芯片作为直接数字频率合成器,通过编程控制合成频率为500 MHz的信号,并利用其镜像频率获得了频率为1 500 MHz的信号。实际操作中,通过对AD9912芯片内部集成的一个48位的频率控制字(FTW)寄存器赋值,为相位累加器提供了一个初始值,在每一个系统周期中,相位累加器都要把输出值与FTW值累加一次,相位累加器输出的数字量进行相符转换后,由14位DAC转换为模拟信号,输出所需正弦波。FTW与AD9912芯片输出的设计频率的关系表达式为:

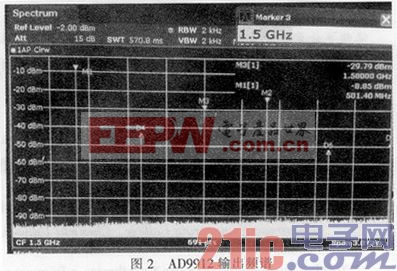

为了合成镜像频率为1 500 MHz信号,由(3)式计算可知须首先合成500 MHz频率,由式(4)计算可知,在参考频率ωS=1 GHz的情况下合成ωDDS=500MHz的设计频率,只需设置FTW=140737488355328(0x800000000000)。最后采用带通滤波器对输出信号进行选频即可获得1 500 MHz信号。

在一般的DDS应用中,由于奈奎斯特采样定理的限制,往往取参考频率的40%作为设计频率,并选用低通滤波器来滤除其它频率杂散。由于本应用中只需利用相应设计频率的UHF镜像频率,可以不考虑设计频率信号的性能,故本硬件系统的合成频率取参考时钟频率的一半500 MHz。在实际得出的频谱图中可以看到当设计频率为500 MHz的时候,存在镜像频率为1500 MHz的信号。

2 硬件系统设计

系统硬件模块主要包括:基于MSP430的单片机控制模块,基于AD9912的直接数字频率合成模块,选频模块。在实际操作中,AD9912芯片输出的合成信号频谱中含有大量的杂散信号分量。其中主要杂散是设计频率的谐波和其他不需要的镜像频率,这些频率分量都可通过窄带滤波的方式去除,但是由于系统的不完善和电源供电谐波的影响,会存在频率靠近1 500 MHz镜像频率的杂散分量。这些杂散分量往往不能被滤波器滤除掉。为避免出现这样的情况,将杂散抑制作为本硬件系统的重点设计内容。

- 一种基于DDS技术的信号发生器研究与实现(03-30)

- ADI常用DDS的线性扫频特性比较研究(04-16)

- 基于DDS+PLL高性能频率合成器的设计与实现(04-24)

- 基于Matlab/DSP Builder任意波形信号发生器的两种设计(03-06)

- 基于DSP的低频频率特性测试仪(03-06)

- DSP和DDS的三维感应测井高频信号源实现(01-23)