S3C2410外围存储系统的研究与设计

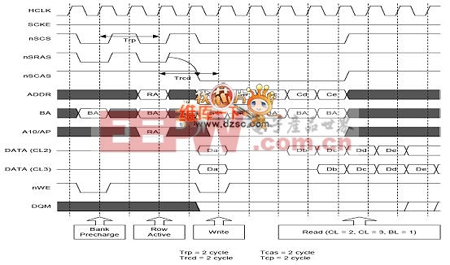

在实际工作中,如图1所示,在第3个总线时钟,nSCS为低电平,表示SDRAM被选中,并且地址线的Bank地址与相应的行地址同时发出,这个命令称之为“行有效”或“行激活”(RowActive)。此时SDRAM将行地址锁存(nSRAS有效),但还没有执行写命令(nWE为高电平),因为没有列地址(nSCAS为高电平),存储单元无法确定。经过Trcd(RAS至CAS延迟)后,SDRAM再次被选中(nSCS为低电平),此时nSCAS为低电平,指示SDRAM此时地址线上的地址为列地址,同时nWE有效,写操作被执行。可见发送列地址寻址命令与具体的操作命令(是读还是写),这两个命令也是同时发出的,所以一般都会以“读/写命令”来表示列寻址,相关的列地址被选中之后,将会触发数据传输。至此,S3C2410对SDRAM的寻址就完成了。可见,S3C2410将地址总线上的地址分成行地址和列地址并分开传输给SDRAM。基于上述的寻址机制,由BA[1:0]和12根地址线就可以寻址32M或更大的地址空间了。

图 1 S3C2410 SDRAM时序图

2 存储器控制器和相关引脚介绍

2.1寄存器介绍

S3C2410存储器控制器主要有:总线带宽和等待控制寄存器(BWSCON);总线控制寄存器(BANKCONN:nGCS0-nGCS5);BANK控制寄存器(BANKCONn:nGCS6-nGCS7);刷新控制寄存器(REFRESH);BANKSIZE寄存器;SDRAM模式寄存器集寄存器(MRSR)等,详情请见参考文献[3]。

2.2相关引脚

S3C2410提供了相关的引脚来控制存储器访问:

组选择信号:nGCS0-nGCS5,nGCS6(nSCS0),nGCS7(nSCS1)引脚用来选择相应的存储器组。

访问控制信号:为了实现ARM存储器访问指令LDR/STR字节、半字和字访问的三种方式,在S3C2410的存储器组中,除了Bank0以外的所有地址空间都可以通过编程设置为8位、16位或32位对准访问,Bank0可以设置为16位或32位。引脚nWBE[3:0](写字节使能)实现8bit ROM芯片组的三种访问方式,或者SRAM不使用UB/LB(在BWSCON中设置)的情况下,与UB/LB连接。引脚nBE[3:0](在使用SRAM情况下的字节允许信号)在SRAM使用UB/LB(是否使用可在BWSCON中设置)的情况下与UB/LB连接。DQM[3:0](SDRAM数据屏蔽信号)引脚实现对SDRAM的三种访问。还有nWAIT、nXBREQ/nXBACK引脚。

3 硬件电路设计

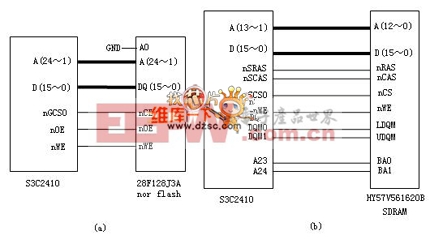

在本嵌入式系统开发实验中,S3C2410扩展的存储系统采用了英国Intel公司的16M E28F128J3A-150 NOR Flash芯片,以及Hynix公司的32M HY57V561620B SDRAM芯片。地址空间分配如下:Flash为Bank0中的0x00000000~0x07FFFFFF地址段,而SDRAM为Bank6中的0x30000000~0x37FFFFFF地址段,具体的电路连接如图2。

图 2 S3C2410 与Flash、SDRAM的电路连接图

4 存储系统初始化

U-Boot是德国DENX小组的开发用于多种嵌入式CPU的开放源代码bootloader程序,目前最新版本是1.1.6,本实验使用的是U-Boot-1.1.4。U-Boot是在ppcboot以及armboot的基础上发展而来,现已非常成熟和稳定,已经在许多嵌入式系统开发过程中被采用。其支持多种目标操作系统,其中对Linux的支持最完善,是嵌入式Linux Bootloader的最佳选择。

由于本实验Linux要移植的开发板是基于s3c2410的开发板,在U-Boot中已有移植成功的smdk2410开发板,故以smdk2410开发板上运行的U-Boot为模板设计适合本实验的U-Boot。有关存储系统的初始化修改如下:

(1)Flash驱动程序采用了board/Cmi/Flash.c,由于cmi中的flash.c在写入时要交换字节,因而删除了它的write_short()和write_buff()函数,利用board/ep7312/Flash.c中的write_word()和write_buff()函数,并且把flash.c中的FLASH_BASE0_PRELIM改为CFG_FLASH_BAS

- 基于s3c2410的CramFS根文件系统的移植(07-13)

- AD7888与S3C2410的SPI接口及Linux下嵌入式驱动的实现(11-06)

- 基于WinCE的ARM视频监控系统(11-14)

- 基于WinCE的I2C驱动程序设计(04-24)

- WinCE下光电编码器的驱动程序设计(04-12)

- 嵌入式Win CE中CAN总线控制器的驱动设计与实现(05-01)