数字秒表电路设计

一、工作原理

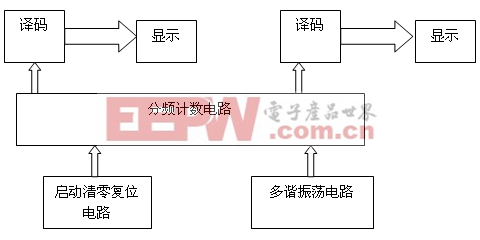

本电路由启动、清零复位电路、多谐振荡电路、分频计数电路、译码显示电路等组成。如下图所示:

启动清零复位电路主要由U6A、U6B、U7B、U7D组成,其本质是一个RS触发器和单稳态触发器。J1控制数字秒表的启动和停止,J2控制数字秒表的清零复位。开始时把J1合上,J2打开,运行本电路,数字秒表正在计数。

当打开J1,合上J2键,J2与地相接得到低电平加到U6B的输入端,U6B输出高电平又加到U6A的输入端,而U6A的另一端通过电阻R15与电源相接得到高电平,(此时U6B与U6A组成RS触发器),U6A输出低电加到U7A的输入端,U7A被封锁输出高电平加到U5的时钟端,因U5不具备时钟脉冲条件,U5不能输出脉冲信号,因此U3、U4时钟端无脉冲而停止计数。当J1合上时,打开J2键,J1与地相接得到低电平加到U6A的输入端,U6A输出高电平加到U6B的输入端,U6B输出低电平加至U7B,使U7B输出高电平,因电容两端电压不能跃变,因此在R7上得到高电平加到U7D输入端,U7D输出低电平(进入暂态)同时加到U3、U4、U5的清零端,使得U3、U4的QD---QA输出0000,经U1、U2译码输出驱动U9、U10显示“00”。因为U7B与U7D组成一个单稳态电路,经过较短的时间,U7D的输出由低电平变为高电平,允许U3、U4、U5计数。同时U6A输出高电平加到U7A的输入端,将U7A打开,让555的3脚输出100KHZ的振荡信号经U7A加到U5的时钟脉冲端,使得U5具备时钟脉冲条件,U5的9、10、7脚接高电平,U5构成十分频器,对时钟脉冲计数。当U5接收一个脉冲时,U5内部计数加1,如果U5接收到第十个脉冲时,U5的15脚(RCO端)输出由低电平跳变为高电平作为U4的时钟脉冲,从而实现了对振荡信号的十分频,产生周期为0.1S的脉冲加至U4的时钟端。U4的9、10、7脚接高电平,当U4接收到来自U5的脉冲时,U4的QD---QA输出0001加到U2的DCBA端,经U2译码输出1001111经电阻R8~R14驱动数码管U10显示,此时数码管显示“1”,当U4计数到1001时,U4的15脚输出高电平接到U7C,经反相后得到低电平,加到U3的时钟脉冲端,U3A不具备时钟脉冲条件,当U4再接收一个脉冲时,U4的输出由1001翻转为0000,此时U4的15脚输出低电平通过U7C反相输出高电平,从而得到一上升沿脉冲加至U3的时钟端,使得U3的QD---QA输出0001加到U1的DCBA输入端,经U1译码输出100111,经电阻R1~R7驱动数码管U9,数码管显示“1”。如此循环的计数,最后数码管U9、U10显示最大值99即9.9秒。

由集成块555、电阻R19、R18、电容C1、C2组成多谐振荡器,当接通电源,电源通过电阻R19与R18对电容C2进充电,当UC2上升到2/3VCC时,集成块555的3脚输出低电平,内部三极管导通,C2通电阻R19进行放电,当UC2下降到1/3VCC时,内部三极管截止,集成块555的3脚输出高电平,接着电源又通过电阻R19与R18对电容C2进充电,当UC2上升到2/3VCC时,集成块555的3脚输出低电平,如此循环的充、放电,555的3脚输出100HZ的矩形方波信号加到U7A的输入端。

二、设计依据

本电路主要采用了二输入与非门74LS00,十进制BCD码计数器74LS160,BCD七段译码器/驱动器7447,555时基集成电路,七段数码管。

利用74LS00可以组成RS触发器,单稳态触发器。其74LS00的逻辑功能是有0出1,无0出0。

其逻辑表达式:Y=/(AB) ,真值表如下:

| A | B | Y |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

十进制BCD码计数器74LS160具备计数分频功能,其真值表如下:

输入 | 输出 | |||||||||||

CLK | CLR | LOAD | EP | ET | A | B | C | D | QA | QB | QC | QD |

X | 0 | X | X | X | X | X | X | X | 0 | 0 | 0 | 0 |

↑ | 1 | 0 | X | X | A | B | C | D | A | B | C | D |

X | 1 | 1 | 0 | X | X | X | X | X | 保持 | |||

X | 1 | 1 | X | 0 | X | X | X | X | 保持 | |||

↑ | 1 | 1 | 1 | 1 | X | X | X | X | 加法计数 | |||

↑ | 1 | 0 | X | X | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

逻辑功能:当CLR,LOAD,EP,ET均接高电平时,时钟CP端每来一个上升沿,计数器在原来的基数上加1,并从QA,QB,QC,QD,输出相应的十进制BCD码。利用74LS160的这个功能特点可以设计出十分频器,计数器。

7447为BCD七段译码器/驱动器,真值表如下:

十进制 | LT | RB | D | C | B | A | BI/RBO | a | b | c | d | e | f | g |

0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

1 | 1 | X | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

2 | 1 | X | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

3 | 1 | X | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

4 | 1 | X | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

5 | 1 | X | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

6 | 1 | X | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

7 | 1 | X | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

8 | 1 | X | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

9 | 1 | X | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 |

7447为四线-七段译码器,可以用来驱动七段共阳极数码管,当LT,RBI,BI,端接高电平时,从DCBA端输入BCD码时,从abcdefg端输出相应的数码管显示码。

共阳七段数码管真值表

A | B | C | D | E | F | G | 显示字符 |

0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

0 | 0 | 1 | 0 | 0 | 1 | 0 | 2 |

0 | 0 | 0 | 0 | 1 | 1 | 0 | 3 |

1 | 0 | 0 | 1 | 1 | 0 | 0 | 4 |

0 | 1 | 0 | 0 | 1 | 0 | 0 | 5 |

1 | 1 | 0 | 0 | 0 | 0 | 0 | 6 |

0 | 1 | 1 | 1 | 1 | 1 | 7 | |

0 | 0 | 0 | 0 | 0 | 0 | 0 | 8 |

0 | 0 | 0 | 1 | 1 | 0 | 0 | 9 |

结合四线-七段译码器7447可以现实0到9个数字。

555时钟电路可以构成多谐振荡器,真值表如下:

| RST | THR | TRI | OUT | TD |

| 0 | X | X | 0 | 导通 |

| 1 | >2\3VCC | >1\3VCC | 0 | 导通 |

| 1 | 2\3VCC | >1\3VCC | 不变 | 不变 |

| 1 | 2\3VCC | 1\3VCC | 1 | 截止 |

| 1 | >2\3VCC | 1\3VCC | 1 | 截止 |

注明:6脚为THR,触发器输入端,低电平有效。

2脚为TRI,阀值输入端,高电平有效。4脚为RST,总复位端,低电平有效。

7脚为DIS,放电端。5脚为CON,控制端。1脚接地,8脚接电源。

3脚为输出端。TD为内部三极管。

三、电路图

- 基于单片机的数字秒表设计(03-07)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)