KCPSM6 PicoBlaze的原理与应用

引言

PicoBlaze 8位嵌入式处理器是Xilinx公司为Virtex、Spartan系列FPGA和CoolRunner—II系列CPLD设计的嵌入式处理器软核。针对不同的器件,Xilinx公司共推出了3个版本的PicoBlaze,包括KCPSM3(目标器件为Spartan 3、Virtex II、Virtex II PRO、Virtex 4和Virtex 5)CPLD版(目标器件为CoolRunner—II)和最新推出的KCPSM6(目标器件为Spartan 6、Virtex 6和7系列FPGA)。KCPSM6针对Spartan 6、Virtex 6和7系列FPGA进行了特殊优化,增加了一些新特性,在开发和调试方法上也与KCPSM3有所不同。本文分析对比了其异同,对KCPSM6在开发调试中的注意事项进行总结,并在Avnet Spartan 6 MicroBoard上进行了实例验证。

1 KCPSM6 PicoBlaze的体系结构

KCPSM6 PicoBlaze(以下简称KCPSM6)8位嵌入式处理器是Xilinx公司为Spartan 6、Virtex 6和7系列FPGA设计的嵌入式处理器软核,它具有效率高、占用资源少等优点,可以方便地嵌入到硬件系统设计中,实现与其他功能模块的无缝连接。它仅占用26个Slice和1个BRAM,占XC6SLX4器件4.3%的资源、XC6SLX150T器件不到0.11%的资源。KCPSM6嵌入式处理器具有高达52~120 MIPS的指令执行速度,具体速度取决于所选用的FPGA所属系列和器件速度等级。

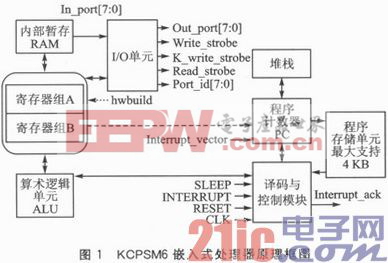

KCPSM6微处理器主要由以下几个单元组成:

◆两组16个8位通用寄存器;

◆最高支持4 KB的程序存储单元;

◆8位算术逻辑单元,带有CARRY和ZERO标志位;

◆64、128或256字节内部暂存RAM;

◆256个输入和256个输出端口,方便扩展应用;

◆中断控制单元;

◆休眠模式,进一步降低系统功耗。

KCPSM6嵌入式处理器的原理框图如图1所示。

KCPSM6新增的特性和功能总结如下:

(1)新增引脚

sleep引脚。当sleep引脚电平由低变高时,KCPSM6在执行完最后一条已读取指令后,进入休眠模式,以降低系统功耗。若将sleep引脚一直置低电平,则KCPSM6一直处于正常工作状态。

K_write_strobe为常量输出触发信号,与OUTPUTK指令配合使用,可用一条指令即可完成向输出端口输出常量值,而无需寄存器的干预。

bram_enable为程序存储单元BRAM使能信号,可进一步降低系统功耗。

Address[11:10]为程序存储单元高位地址线,最大支持4 KB程序存储。

(2)新增属性

KCPSM6新增了3个属性,分别是hwbuild(与HWBULID指令配合使用,可用于定义软件版本等功能)、interrupt_vector(定义中断矢量,默认为0x3FF)和scratch_pad_memory_size(定义内部暂存RAM大小,默认为64 B)。

(3)新增指令

KCPSM6指令集向下兼容KCPSM3的指令集,并新增了9条指令,分别是TESTCY、COMPARECY、REGBANK、STAR、OUTPUTK、JUMP@、CALL@、LO ADRETURN和HWBULID。新指令的扩展,极大地改善了KCPSM6的编程灵活性和代码效率。例如,向端口0x01输出0x5A,在KCPSM3中需执行两条指令:“LOAD s0,5A”和“OUPUT s0,01”。而在KCPSM6中,只需执行“OUTPUTK 5A 01”即可。其他新增指令的详细功能,见参考文献。

2 KCPSM6开发与调试

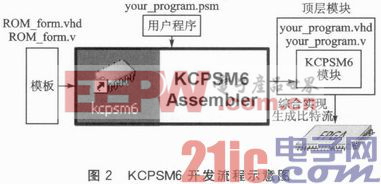

KCPSM6的开发流程与KCPSM3基本相同。KCPSM6的开发流程如图2所示。

如图2所示,用户程序和ROM模块经编译器KCPSM6 Assembler编译后,生成包含程序代码的ROM模块。在顶层模块中例化ROM模块和KCPSM6模块,然后综合、实现并生成比特流下载到FPGA中。在程序调试过程中,经常需要对用户程序进行反复修改,如果采用常规的方法,则每次修改用户程序,都要重新综合、布局布线,生成新的比特文件,往往需要几分钟到十几分钟,耗时耗力,给调试带来了极大不便。为此,与KCPSM3类似,Xilinx公司也为KCPSM6提供了JTAG Loader工具,而采用JTAG Loader进行调试则无需重新综合、布局布线,通过JTAG接口直接修改PicoBlaze的程序BRAM,只需几秒即可完成程序更新,大大加快了调试进度。

JTAG Loader的使用步骤如下:

①将代码中的C_JTAG_LOADER_ENABLE属性设为“1”。

②综合、实现生成比特流并下载到FPGA中。

③将JTAG Loader.exe复制到当前工程目录下。

④打开命令提示符,并切换到当前目录,运行JTAGLoader(如果是64位操作系统则运行JTAG Loader64),JTAG Loader自行识别目标FPGA,如果报错显示未知器件,则需要输入其IR_Length参数,该参数可以在ISE安装目录下查到,如:C:\Xilinx\13.2\ISE_DS\ISE\acecf\data\xccace.bsd文件中的attribute INSTRUCTION_LENGTH ofXCCACE:entity is 8,其他器件的查阅方法类似。

⑤修改用户程序,并用kcpsm6.exe重新编译程序。

⑥运行jtagloader—1 your_program.hex,即可实现一键更新程序。

另外,值得注意的是,使用JTAG Loader之前,必须正确设置系统的环境变量,具体方法是运行ISE安装目录下C:\Xilinx\1 3.2\ISE_DS文件夹内的settings32.bat批处理文件即可。

3 应用实例

为了验证KCPSM6的新增功能及JTAG Loader的使用方法,本文在FPGA开发板上实现了8位LED的控制。综合结果显示,本设计共占用了35个Slice和2个RAMB 16BWERs单元,仅占XC6SLX75T-3FGG676总Slice数和BRAM单元的1%。最后,将生成的比特流下载到开发板上进行验证,LED能够按预期要求闪烁。修改用户程序,重新编译后,能够用JTAG Loader快速更新程序。

结语

本文简要阐述了Xilinx公司最新推出的KCPSM6软核的结构及原理,并与KCPSM3进行了对比分析。介绍了KCPSM6的开发调试流程,并进行了实例验证。本文对已有KCPSM3使用经验的设计者快速熟悉KCPSM6的应用开发具有积极意义。

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- SHARC引领第四代通用DSP高端应用潮流(09-27)

- 在应用可编程测控网络设计(03-15)

- 基于dsPIC33F系列单片机的应用程序升级方法(04-03)

- 采用混合时钟模式提高Linux时钟精度的方法(05-10)

- MSP430低功耗原理及其在海温测量中的应用(06-06)