基于多处理器的可识别方位引信信号处理系统

摘要 设计了一种采用FPGA+DSP系统框架的信号处理机,由3个核心处理器协同工作,共同完成多通道多普勒信号的目标检测和方位识别等功能。该信号处理机在实现频域目标检测功能的同时,实现了8象限的方位识刺功能,能够提高引战配合效率。多处理器的分层设计保证了该信号处理机的实时性和灵活性,是一个具有较强可扩展性的信号处理开发平台。

关键词 多处理器;方位识别;单元平均恒虚警;实时性

在现代战争模式中,导弹定向爆破能大幅提高作用于目标方向的杀伤能量,使导弹获得更大的命中和毁伤概率、作战能力。引信作为导弹的重要组成部件,具有方位识别能力是实现导弹定向爆破的前提条件。信号处理系统作为引信的核心部件,是方位识别功能和目标检测功能的主要实现单元。其结构和性能对引信的整体性能有着至关重要的影响。随着FPGA、DSP技术的发展,数字信号处理技术在引信中的应用大幅增强了引信信号的处理能力,有利于方位识别引信的实现。文中在采用FPGA+DSP架构的基础上,实现一种具有8象限方位识别能力的引信信号处理机。

1 可识别方位引信系统原理

本方位识别算法旨在实现引信周向8个象限的方位识别,利用双收双发收发分离共4根天线,在导弹圆周方向形成360°均匀探测场。其布局如图1所示,T1/T2为发射天线,R1/R2为接收天线,根据方位识别算法,可实现Q1~Q8共8个象限的方位识别。

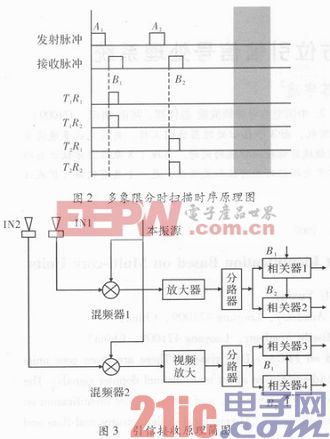

根据时分复用原理得到4个通道的多普勒信号,是多象限分时扫描的最终目的。算法中的多象限分时扫描采用接收支路同时接收回波,再利用接收脉冲相关特性将接收到的回波进行分离,这种定向探测系统实现相对简单,收发隔离度高,并且能够降低回波多普勒的距离副瓣。图2为多象限分时扫描时序原理图,图3为引信系统实现框图。

2 信号处理系统设计

2.1 功能要求

设计中定向探测引信的信号处理器是一个功能复杂的处理器,采用数字频域处理方式实现,包括A/D转换电路及信号处理模块,实现对多普勒信号的采样、量化,数字信号的FFT、CFAR处理,完成对目标的检测、启动判断、干扰判别。其功能包括:(1)对4路多普勒信号进行数字化。(2)依据4路多普勒信号,实现时频转换及相关频域处理。(3)在符合目标检测判据时给出目标存在信号。(4)将多普勒信号的频域峰值作为目标能量信息,对4路目标能量信息进行比较,实现引信周向8个象限的方位识别。

2.2 数宇信号处理系统工作原理

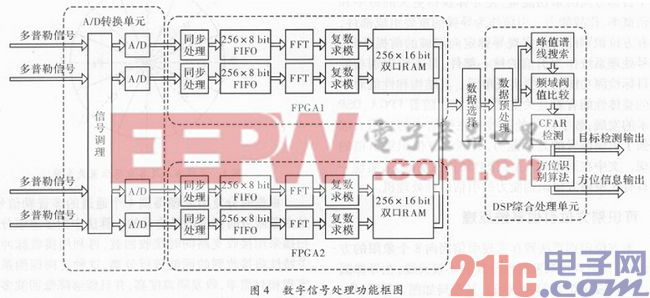

目标或环境回波经过引信接收前端,根据分时扫描原理得到4路多普勒回波,4路信号同时输入信号处理电路。4路多普勒信号首先经过A/D采样,形成回波时域数据,然后进行FFT频域分析和坐标系转换,基于线性逼近近似算法的求模运算、多处理器协同工作下的数据传输缓存,最终输入DSP芯片中进行目标检测和方位识别,得如果满足一定的信噪比则给出目标存在信号,在目标存在的前提下继续进行目标方位识别,输出目标方位信息。设计信号处理系统采用了FPGA+DSP架梅,由FPGA完成4路FFT运算,由DSP完成目标检测、脱靶方位识别,由2片FPGA芯片和单片DSP芯片梅成了一个多处理器协同工作的数字信号处理机。图4给出了本设计中引信信号处理单元的流程框图。

2.3 FPGA单元设计

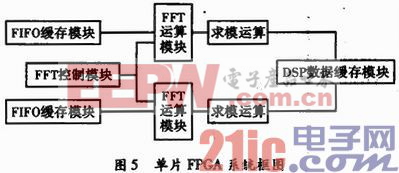

引信信号处理系统中两片FPGA芯片,主要实现4路多普勒信号的时频域转换以及频域信息的预处理,要求4路并行处理。FPGA芯片选用两片Altera公司的EP1K100QI208—2,分别记为FPGA1和FPGA2,单片FPGA进行两路FFT运算、求模运算以及计算结果的缓存。模块化思想能够大幅优化数字信号处理系统设计,增强代码的可读性和维修性,设计中广泛采用了模块化设计思想,对信号处理中的各项功能合理划分。单片FPGA内部主要包含FIFO缓存模块、FFT时频转换模块、求模运算模块、DSP数据缓存模块。图5为单片FPGA内部系统框图。

2.4 DSP单元设计

引信信号处理系统设计中选用了TI公司的F2802芯片,作为FFT运算后续处理检测、判别的主处理器。F2812有内置Flash存储器,无需外挂存储芯片。F2812是一款高速成熟的DSP处理器,具有很强的数字信号处理能力,最高核心频率可达150 MHz,程序中系统时钟设定为100 MHz,既能满足信号处理的实时性要求,同时又保证了器件工作的稳定性。

DSP信号处理器接收到FPGA发送的中断请求后,从FPGA双口RAM中读取128点频谱x(k),对x(k)进行逐点选大,找到目标所在频谱位置。将单元内其他谱线能量相加平均作为噪声能量N。为弱化信号截断引起的频谱泄漏,计算噪声能量时,去掉最大谱线两侧相邻的两根谱线,将最大谱线及噪声能量的比值与既定门限进行比较,判断目标是否存在,若不存在,则进行下一帧运算;若存在,则进入方位识别程序,进行方位识别,若能识别出目标方位,则给出二进制3位方位指示信号3b000~3b111,分别对应导弹周向8个方位。DSP软件处理流程图如图6所示。

信号 处理 理系 引信 方位 处理器 识别 基于 相关文章:

- 用CPLD实现FIR数字滤波器的设计(08-07)

- FPGA和DSP明帮暗战,争夺20亿美元高性能信号处理市场(08-17)

- Altera FPGA在Fairlight新媒体处理引擎中替代64片DSP(01-20)

- 基于DSP的短波分集合成接收机(09-01)

- 数字信号处理器TMS320F241在变频空调中的应用(04-28)

- 数字信号控制器在变频家电中的应用(05-15)