51单片机 P0口工作原理详细讲解

出低电平后,锁存器Q=0,Q非=1,场效应管T2开通,端口线呈低电平状态。此时无论端口线上外接的信号是低电乎还是高电平,从引脚读入单片机的信号都是低电平,因而不能正确地读入端口引脚上的信号。又如,当从内部总线输出高电平后,锁存器Q=1,Q非=0,场效应管T2截止。如外接引脚信号为低电平,从引脚上读入的信号就与从锁存器读入的信号不同。为此,8031单片机在对端口P0一P3的输入操作上,有如下约定:为此,8051单片机在对端口P0一P3的输入操作上,有如下约定:凡属于读-修改-写方式的指令,从锁存器读入信号,其它指令则从端口引脚线上读入信号。

读-修改-写指令的特点是,从端口输入(读)信号,在单片机内加以运算(修改)后,再输出(写)到该端口上。下面是几条读--修改-写指令的例子。

ANL P0,#立即数;P0→立即数P0

ORL P0,A ;P0→AP0

INC P1 ;P1+1→P1

DEC P3 ;P3-1→P3

CPL P2 ;P2→P2

这样安排的原因在于读-修改-写指令需要得到端口原输出的状态,修改后再输出,读锁存器而不是读引脚,可以避免因外部电路的原因而使原端口的状态被读错。

P0端口是8031单片机的总线口,分时出现数据D7一D0、低8位地址A7一AO,以及三态,用来接口存储器、外部电路与外部设备。P0端口是使用最广泛的I/O端口。

2、作为地址/数据复用口使用时的工作原理

在访问外部存储器时P0口作为地址/数据复用口使用。

这时多路开关‘控制’信号为‘1’,‘与门’解锁,‘与门’输出信号电平由“地址/数据”线信号决定;多路开关与反相器的输出端相连,地址信号经“地址/数据”线→反相器→V2场效应管栅极→V2漏极输出。

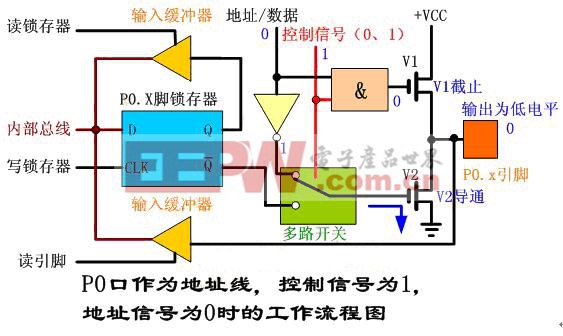

例如:控制信号为1,地址信号为“0”时,与门输出低电平,V1管截止;反相器输出高电平,V2管导通,输出引脚的地址信号为低电平。请看下图(兰色字体为电平):

反之,控制信号为“1”、地址信号为“1”,“与门”输出为高电平,V1管导通;反相器输出低电平,V2管截止,输出引脚的地址信号为高电平。请看下图(兰色字体为电平):

可见,在输出“地址/数据”信息时,V1、V2管是交替导通的,负载能力很强,可以直接与外设存储器相连,无须增加总线驱动器。

P0口又作为数据总线使用。在访问外部程序存储器时,P0口输出低8位地址信息后,将变为数据总线,以便读指令码(输入)。

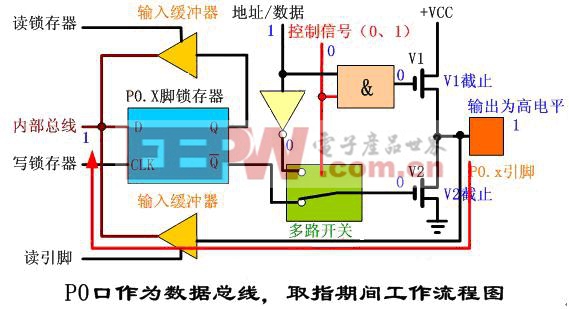

在取指令期间,“控制”信号为“0”,V1管截止,多路开关也跟着转向锁存器反相输出端Q非;CPU自动将0FFH(11111111,即向D锁存器写入一个高电平‘1’)写入P0口锁存器,使V2管截止,在读引脚信号控制下,通过读引脚三态门电路将指令码读到内部总线。请看下图

如果该指令是输出数据,如MOVX @DPTR,A(将累加器的内容通过P0口数据总线传送到外部RAM中),则多路开关“控制”信号为‘1’,“与门”解锁,与输出地址信号的工作流程类似,数据据由“地址/数据”线→反相器→V2场效应管栅极→V2漏极输出。

如果该指令是输入数据(读外部数据存储器或程序存储器),如MOVX A,@DPTR(将外部RAM某一存储单元内容通过P0口数据总线输入到累加器A中),则输入的数据仍通过读引脚三态缓冲器到内部总线,其过程类似于上图中的读取指令码流程图。

通过以上的分析可以看出,当P0作为地址/数据总线使用时,在读指令码或输入数据前,CPU自动向P0口锁存器写入0FFH,破坏了P0口原来的状态。因此,不能再作为通用的I/O端口。大家以后在系统设计时务必注意,即程序中不能再含有以P0口作为操作数(包含源操作数和目的操作数)的指令。

- 关于RTX51 TINY的分析与探讨(05-30)

- 浅析8051模块化编程技巧(05-28)

- 基于DSP和单片机通信的液晶显示设计方案(07-20)

- 锁相环控制及初始化简析(08-27)

- 基于MSP430自动胀管控制器的研究(09-07)

- 嵌入式C实现延时程序的不同变量的区别(03-01)