基于ARMS和FPGA的嵌入式数控系统设计

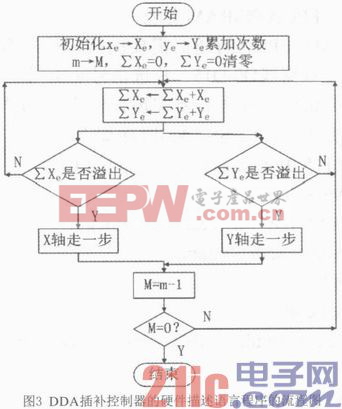

4.2 数字积分插补的FPGA实现

采用有限状态机的设计方法,每个轴的数字积分插补均由一个三状态机的积分累加器完成。本系统的FPGA开发环境为Xilinx公司的Xil inx ISE,并结合ModelSim仿真软件对整个系统进行了全面的功能验证。如图4所示为DDA插补模块的顶层RTL级原理图,由图5可知DDA插补模块的输入信号为各轴的起始坐标以及时钟信号和启动信号,输出信号为各轴的脉冲信号和方向信号。

运用ModelSim仿真软件对DDA插补模块进行仿真验证。测试数据的起点坐标为(0,0,0)终点坐标为(8,15,11),仿真结果如图5所示,显示系统很好的完成了三轴的脉冲分配。

4.3 加减速控制模块

加减速控制是数控系统的关键技术之一,也是实现数控系统高实时性的瓶颈。数控系统中,为了保证机床在启动或停止时不产生冲击、失步、超程或振荡,必须对进给电机的脉冲频率或电压进行加减速控制。即当机床加速启动时,保证加在电机上的脉冲频率逐渐增加;而当机床减速停止时,保证加在电机上的脉冲频率逐渐减小。目前,电机加减速的常用控制方法是梯形加减速控制和S形加减速控制。本次设计采用两种控制方案以适应不同工作场合的要求。

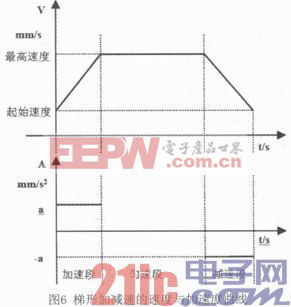

4.3.1 梯形加减速

梯形加减速是指在加减速过程中加速度为常数,速度曲线为梯形的加减速过程。梯形加减速控制算法简单、易于实现,但在加减速过程中加速度曲线不连续会导致驱动机构的振动和冲击。正常情况下梯形加减速运动过程如图6所示分为加速段、匀速段和减速段三个阶段。

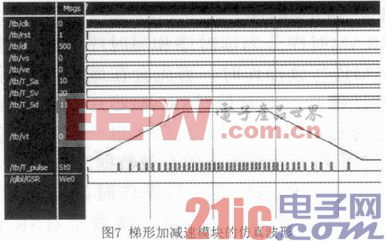

图7所示为ModelSim对梯形加减速模块的仿真结果,可以看到插补器输出的脉冲速度曲线呈现梯形,输出脉冲的频率的大小随速度的变化而变化,实现了电机的梯形调速。

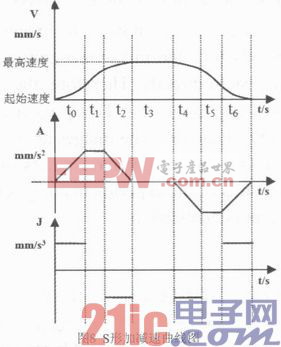

4.3.2 S形加减速

S形加减速是指在加减速时,加速度导数为常数,速度曲线为S形曲线的加减速过程。通过控制加速度导数来避免加速度突变,减小加工过程中由于加速度突变引起的机械系统振动。S形曲线速度控制可以得到平滑的速度曲线,但算法复杂,运算时间长。

S形加减速中加速度相对加速度导数的变化规律相当于直线加减速中速度相对加速度的变化规律。如图8所示为S形曲线加减速的曲线图,图中从上到下依次为速度曲线、加速度曲线以及减速度曲线。从图中可以看出,正常情况下S形加减速分为:加加速段、匀加速段、减加速段、匀速段、加减速段、匀减速段和减减速段七个阶段。加速度连续,调速光滑,不会导致驱动机构的振动和冲击。

图9所示为ModelSim对S形加减速模块的仿真结果,可以看到插补器输出的脉冲速度曲线呈现梯形,输出脉冲的频率的大小随速度的变化而变化,实现了电机的S形调速。

5 结束语

本文给出了一种基于ARM和FPGA的开放性的嵌入式数控系统,突破了传统的计算机数控系统架构,采用ARM处理器S3C2440A和FPGA器件XC3S25 0E和μC/OS-II嵌入式实时操作系统组成的数控系统软硬件平台,充分利用了ARM微处理器的高速运算能力与FPGA的快速配置能力,大大减少了系统的外围接口器件,并具有良好的稳定性、模块化、可扩展性、可移植性等特点,有利于实现数控系统的开放化和网络化,有效地降低了系统成本,适合我国数控系统发展的需要,具有广阔的应用前景。

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于ARM体系的嵌入式系统BSP的程序设计方案(04-11)

- 在Ubuntu上建立Arm Linux 开发环境(04-23)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- SQLite嵌入式数据库系统的研究与实现(02-20)

- 革新2410D开发板试用手记(04-21)