基于PCI 总线的DSP 系统应用程序的更新

0 引言

在DSP嵌入式业务系统设备中,一般采用片外FLASH自举方式来实现DSP端应用程序的加载和启动。当DSP业务系统需要更新应用程序时,则可通过仿真器连接JTAG 口来控制DSP,完成DSP 外围FLASH 的应用程序更新。然而,对于成型、交货的设备产品,DSP业务系统板上一般不会留有JTAG口,或在机箱中很难插拔仿真器;另一方面,对已交货产品经常插拔仿真器,会对硬件设备有所损伤,使设备硬件处于非控状态。

如果系统设计使用了PCI作为系统通信总线,则可以通过PCI来完成DSP 业务系统应用程序的更新和加载。本设计以TI公司TMS320C6416T(简称C6416)芯片为例,来说明通过PCI总线来更新DSP系统应用程序的过程;同时本文也设计了一种C6416的上电启动方式。

1 C6416 的PCI 特性

1.1 C6416 PCI传输机理

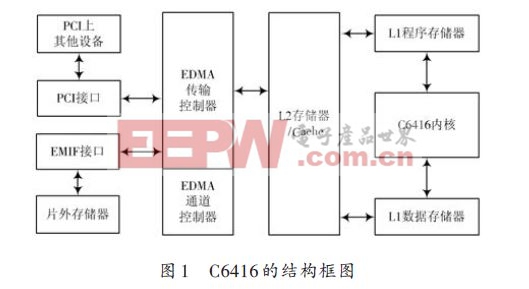

C6416 片内集成了PCI 的控制器,通过PCI 接口C6416可以完成同PCI总线上其他设备的数据交换。图1描述了C6416的结构框图。PCI接口通过EDMA 控制寄存器可以访问C6416的片内存储器/Cache,或者通过EMIF接口访问片外存储器。

从图1可看出,PCI和EMIF接口都是通过EDMA传输控制器来与L2存储器/Cache联系的。EDMA 传输控制寄存器主要用来控制L2存储器和设备外围间的数据通信,包括传输请求队列、地址产生器等;而通道控制器是用户可编程部分,用户可以设置相应的寄存器,方便的设置数据传输方式(一维、二维)、事件触发选择、传输通道选择等。

所有的EDMA传输请求可以由L2控制器、HPI/PCI和EDMA 通道三种渠道发出。一个传输请求一旦递交,将通过链接通道移送到传输交叉开关(TC),在这里它将进行优先级设置与处理。请求链为请求提供了一个内在的优先机制。假定一个请求在同一周期中只递交一次请求,那么靠近TC的首先到达,最远的最后到达。

但进入TC的请求,则会进入传输请求队列,按照队列优先级进行相应处理,如图2所示。

HPI/PCI自动产生传输请求来响应主机。这些请求具有Q2优先级且对用户是不可见的。HPI/PCI递交请求来进行固定模式的单一单元读、写和短数据猝发递增传输操作。

1.2 C6416 PCI操作原理C6416的PCI操作可以设置为:

主模式写:DSP主设备通过PCI接口写数据到外部PCI从设备。

主模式读:DSP 主设备通过PCI接口从外部PCI从设备读数据。

从模式写:外部PCI主设备通过PCI接口写数据到DSP从设备。

从模式读:外部PCI主设备通过PCI接口从DSP从设备读数据。

1.2.1 C6416 PCI寄存器

PCI接口有以下3种寄存器:PCI配置寄存器,PCI I/O 寄存器和映射在DSP 存储空间的PCI 控制状态寄存器。前两类寄存器只能被外部主机访问,DSP从机是不能访问的;而最后一类寄存器,DSP从机是可以访问的,并利用其来完成PCI通信的控制和操作。

PCI配置寄存器包含标准的PCI配置信息,包括设备标识,供应商标识,版本等信息,其可以在上电复位时自动访问E2PROM 进行加载或上电复位时可以通过默认值初始化。

PCI I/O寄存器可以被主机用来对从机进行操作和状态监控。主机通过base2 存储空间来访问该类寄存器。该空间大小为16 B,有三个寄存器:主机状态寄存器(HSR),主机-DSP控制寄存器(HDSR)和DSP页寄存器(DSPP)。

1.2.2 C6416 PCI存储器映射

PCI端口通过3种基址寄存器可以完全访问DSP的存储器映射。

Base0:4 MB 的可预存取空间,通过设置DSP 页寄存器映射来对应所有DSP存储空间,如图3所示。可以理解为,一个4 MB大小的存储窗口,来遍历整个DSP的存储映射区,而DSP 页寄存器的值则决定了这个4 MB存储窗的起始地址。如图4所示。

Base1:8 MB的非预取址映射。其访问起始地址固定,为0×01800000,该存储空间映射为DSP 片内寄存器。如图5所示。

Base2:PCI 16 B I/O 寄存器,上已介绍。

上电后PCI 主机将遍历整个PCI 总线,建立一棵PCI总线树,然后对每个PCI总线树上的结点(设备)进行上述3 个基地址的分配。利用这3 个基地址,PCI主机即可以访问PCI总线上的从设备的全部存储空间。

1.2.3 PCI中断

如果设置了PCIIEN 对应的中断使能位,当对应的中断源产生,DSP将进入中断状态。所有的中断事件对应于一个CPU中断:DSPINT.可以通过PCIIS中断源寄存器来判断产生中断的中断源。

1.2.4 PCI引导

PCI接口支持从PCI总线引导DSP启动。当其他设备从复位状态唤醒后,CPU被复位。在此期间,PCI主机可以尽可能的通过PCI初始化DSP内存。当PCI主机完成所需要的初始化工作,则向I/O寄存器HDCR.DSPINT位写1,使DSP 核退出复位。DSP 则从地址0 处开始运行。值得注意是的是,当C6416 使用PCI 引导方式时,需要通过硬件设置来配置DSP 上电

- 用双端口RAM实现与PCI总线接口的数据通讯(05-06)

- 基于PCI总线和DSP芯片的图像处理平台的硬件设计(07-06)

- 基于DSP和PCI总线的通用数字信号处理系统(11-13)

- 一种基于PCI总线和DSP技术的虚拟仪器设计(03-16)

- 基于Linux平台的天气雷达高速数据采集系统设计(03-13)

- 基于DSP与PC机的PCI总线高速数据传输 (07-08)