基于飞思卡尔QorIQ Qonverge处理器宏/微蜂窝基站带来网络通信新体验

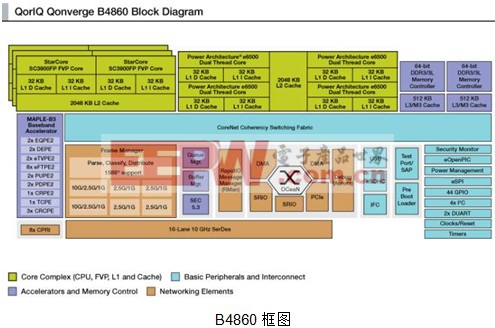

500双线程Power Architecture处理器内核,实现61000处理器CoreMark。六个定点及浮点SC3900FP DSP内核可达到每秒2304亿次加乘运算(GMACS)的定点性能和每秒1152亿次浮点运算(GFLOPS)性能。配合嵌入e6500内核的四个AltiVec SIMD引擎,总计可达到每秒1728亿次浮点运算的IEEE 754浮点性能。功能强大的可编程内核与内置IP数据包处理和安全加速引擎的结合,提供了出色的灵活性和卓越的处理性能,并促进了需要高效节能系统具备大规模处理性能的应用开发。 B4860支持功能强大的片上系统计算资源。B4860片上系统集成了面向多用途片上系统的高速标准接口系列,其中包括两个10 Gbps XFI/XAUI以太网控制器、四个2.5 Gbps/1 Gbps SGMII以太网控制器、两个支持5G下8通道的Serial RapidIO v2.1控制器、和一个支持5G下4通道的PCI Express Gen2控制器。另外还包括两个DDR3/3L控制器、1.867GHz下64/72位检错纠错、NAND/NOR闪存控制器、I2C、SPI、SDHC、USB和UART接口。 B4420器件则集成了两个1.6GHz的双线程Power Architecture e6500处理器内核、两个1.2GHz的StarCore数字信号处理器(DSP) SC3900灵活矢量处理器内核以及支持L1加速的高效基带多加速器平台引擎(MAPLE-B)和支持L2和传输处理的加速器,实现了性能上的飞跃。B4420可提供最多两个20MHz的LTE扇区、600Mbps的吞吐量和具有最佳功率/成本比的中继支持,使设计人员可以开发具有较高的用户密度、低成本和低功率设计的基站。 B4420片上基站旨在帮助运营商适应以数据为中心的4G无线设备的迅速采用,同时降低3G部署的相关成本。它提供了一个综合的高性价比的处理解决方案,支持L1传输基带处理,从回程IP数据包到天线IQ样本。高速且符合行业标准的接口提供面向天线、Wi-Fi芯片集和回程的无缝连接。 引入浮点技术 飞思卡尔对面向宏蜂窝的产品系列不断进行性能提升。日前,飞思卡尔又在其B4产品B4860和B4420系列中添加了先进的浮点技术,推出了面向工业控制和通用市场的新的解决方案,这也是首批引入浮点运算的B4家族成员。 在数据爆炸时代,基站通信处理器需要满足更加密集的数据计算和处理能力,超越计算密集型应用,如雷达、医疗和媒体影像、Cloud-RAN网络架构中的MAC调度程序处理、视频分析、安全、工业自动化及测试测量系统等,这些应用对高精度数值计算有着极其严格的要求。 引入先进的浮点运算可以支持计算密集型任务。为此,业界性能水平最高的定点DSP内核—飞思卡尔SC3900处理单元引入了浮点运算。浮点运算功能与QorIQ Qonverge片上系统集成的多项先进技术实现互补,其中包括高性能处理、安全和网络处理加速引擎。 B4860和B4420片上系统的量产版在引入浮点支持的同时,保留了与现有SC3900内核的二进制代码兼容。这样,已经针对这些片上系统开发软件的客户可享有开发延续性。 与许多其他的异构多核架构不同,B4家族提供完备的缓存一致系统,使本地缓存存储的共享资源保持数据一致性,这种数据一致性不仅体现在内核集群中的L1和共享L2缓存之间,还体现在不同类型的内核集群和外部接口之间,无需软件干预。这一性能的提升简化了多核编程,大大加快了产品上市时间。 B4860和B4420片上系统以及支持飞思卡尔浮点技术的评估板预计于2013年第三季度上市。 面向QorIQ Qonverge B4系列的开发工具 飞思卡尔针对B4860的开发生态合作体系包括基于Eclipse技术的CodeWarrior集成开发环境(IDE),提供完备的多核开发平台。可选工具包括B4860QDS和B4420QDS开发板、面向Power Architecture和StarCore内核的C优化编译器、源代码级多核调试器、设备和内核软件仿真器、优化的设备驱动、Linux® SDK以及用于配置和程序/数据跟踪的软件分析工具。此外,飞思卡尔及其合作伙伴网络还提供配备BSP和SDK的MPU及DSP高效操作系统,其中包含优化的设备驱动。 飞思卡尔也提供了丰富的产品和服务生态系统来支持B4420系列,包括基于Eclipse技术、提供综合多核开发环境的CodeWarrior集成开发环境(IDE)。可用的工具包括QorIQ Qonverge开发系统(QDS)板、面向Power Architecture和StarCore架构的C-optimizing编译器,以及可洞悉源代码执行情况的分析器和调试器。此外,飞思卡尔的合作伙伴网络提供高效的DSP和MPU操作系统,带有BSP和经过优化的设备驱动程序。

飞思卡尔 QorIQ 宏蜂窝 微蜂窝基站 B4860 相关文章:

- 飞思卡尔采用最新平板设计改进第二代智能本外观(01-06)

- DSP系列为下一代无线基站部署提供更高的性能支持(01-07)

- SoC:IP是新的抽象(10-24)

- 如何采用门控时钟来设计低功耗时序电路(06-23)

- 支持ASIL D 应用的安全集成硬件解决方案(12-20)

- 基于飞思卡尔DZ60的AD 1302 KEY 485 CAN FLASH LCD程序(12-01)