嵌入式系统基础之:ARM处理器硬件开发平台

书所采用的硬件平台是深圳优龙科技有限公司的开发板FS2410(如图4.10所示),它的中央处理器是三星公司的S3C2410X。S3C2410X是使用ARM920T核、采用0.18mm工艺CMOS标准宏单元和存储编译器开发而成的。由于采用了由ARM公司设计的16/32位ARM920TRISC处理器,因此S3C2410X实现了MMU和独立的16KB指令和16KB数据哈佛结构的缓存,且每个缓存均为8个字长度的流水线。它的低功耗、精简而出色的全静态设计特别适用于对成和功耗敏感的领域。

S3C2410X提供全面的、通用的片上外设,大大降低系统的成本,下面列举了S3C2410X的主要片上功能。

n 1.8VARM920T内核供电,1.8V/2.5V/3.3V存储器供电;

n 16KB指令和16KB数据缓存的MMU内存管理单元;

n 外部存储器控制(SDRAM控制和芯片选择逻辑);

n 提供LCD控制器(最大支持4K色的STN或256K色TFT的LCD),并带有1个通道的LCD专用DMA控制器;

n 提供4通道DMA,具有外部请求引脚;

n 提供3通道UART(支持IrDA1.0,16字节发送FIFO及16字节接收FIFO)/2通道SPI接口;

n 提供1个通道多主IIC总线控制器/1通道IIS总线控制器;

n 兼容SD主机接口1.0版及MMC卡协议2.11版;

n 提供2个主机接口的USB口/1个设备USB口(1.1版本);

n 4通道PWM定时器/1通道内部计时器;

图4.10优龙FS2410开发板实物图

n 提供看门狗定时器;

n 提供117个通用I/O口/24通道外部中断源;

n 提供不同的电源控制模式:正常、慢速、空闲及电源关闭模式;

n 提供带触摸屏接口的8通道10位ADC;

n 提供带日历功能的实时时钟控制器(RTC);

n 具有PLL的片上时钟发生器。

S3C2410X系统结构图如图4.11所示。

下面依次对S3C2410X的系统管理器、NandFlash引导装载器、缓冲存储器、时钟和电源管理及中断控制进行简要讲解,要注意,其中所有模式的选择都是通过对相关寄存器特定值的设定来实现的,因此,当读者需要对此进行修改时,请参阅三星公司提供S3C2410X用户手册。

1.系统管理器

S3C2410X支持小/大端模式,它将系统的存储空间分为8个组(bank),其中每个bank有128MB,总共为1GB。每个组可编程的数据总线宽度为8/16/32位,其中bank0~bank5具有固定的bank起始地址和结束地址,用于ROM和SRAM。而bank6和bank7是大小可变的,用于ROM、SRAM或SDRAM。这里,所有的存储器bank都具有可编程的操作周期,并且支持掉电时的SDRAM自刷新模式和多种类型的引导ROM。

2.nandflash引导装载器

S3C2410X支持从nandflash存储器启动,其中,开始的4KB为内置缓冲存储器,它在启动时将被转载(装载or转载)到SDRAM中并执行引导,之后该4KB可以用作其他用途。

图4.11S3C2410X系统结构图

| Flash是一种非易失闪存技术。Intel于1988年首先开发出NorFlash技术之后,彻底改变了原先由EPROM和EEPROM一统天下的局面。紧接着,1989年东芝公司发布了NandFlash结构,强调降低每比特的成本、更高的性能,并且像磁盘一样可以通过接口轻松升级。 NorFlash的特点是芯片内执行(ExecuteInPlace),这样应用程序可以直接在Flash闪存内运行,而不必再把代码读到系统RAM中。NorFlash的传输效率很高,在1~4MB的小容量时具有很高的成本效益,但是很低的写入和擦除速度大大影响了它的性能。 Nandflash结构能提供极高的单元密度,可以达到高存储密度,NAND读和写操作采用512字节的块,单元尺寸几乎是nor器件的一半,同时由于生产过程更为简单,大大降低了生产的成本。NAND闪存中每个块的最大擦写次数是100万次,是NorFlash的10倍,这些都使得NandFlash越来越受到人们的欢迎。 |

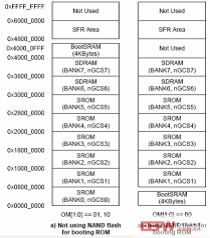

同时,S3C2410X也支持从外部nGCS0片选的Norflash启动,如在优龙的开发板上将JP1跳线去掉就可从NorFlash启动(默认从NandFlash启动)。在这两种启动模式下,各片选的存储空间分配是不同的,如图4.12所示。

图4.12S3C2410两种启动模式地址映射

3.缓冲存储器

S3C2410X是带有指令缓存(16KB)和数据缓存(16KB)的联合缓存装置,一个缓冲区能够保持16字的数据和4个地址。

4.时钟和电源管理

S3C2410X采用独特的时钟管理模式,它具有PLL(相位锁定环路,用于稳定频率)的芯片时钟发生器,而在此,PLL又分为UPLL和MPLL。其中UPLL时钟发生器用于主/从USB操作,MPLL时钟发生器用于产生主时钟,使其能以极限频率203MHz(1.8V)运行。

S3C2410X的电源管理模式又分为正常、慢速、空闲和掉电4种模式。其中慢速模式为不带PLL的低频时钟模式,空闲模式始终为CPU停止模式,掉电模式为所有外围设备全部掉电仅内核电源供电的模式。

另外,S3C2410X对片内的各个部件采用独立的供电方式。

n 1.8V的内核供

ARM处理器 ARM9 嵌入式系统 哈佛结构 S3C2410 相关文章:

- 关于对ARM处理器中“8位位图”的理解(12-01)

- ARM处理器工作模式(11-28)

- ARM处理器模式介绍和模式切换(11-28)

- ARM处理器的总线信号(11-27)

- 选择ARM处理器,ARM7还是Cortex-M3(11-27)

- GNU ARM汇编--(三)ARM处理器的基本原则(11-26)

小知识

小知识